# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

### FACULTAD DE INGENIERÍA

# OBTENCIÓN DE SEÑALES E IMÁGENES MEDIANTE MUESTREO PASOBANDA

T E S I S

QUE PARA OBTENER EL TÍTULO DE: INGENIERO ELÉCTRICO – ELECTRÓNICO P R E S E N T A JOSÉ ALBERTO LLAVOT LÓPEZ

Y PARA OBTENER EL TÍTULO DE: INGENIERO EN COMPUTACIÓN P R E S E N T A REMIGIO ANTONIO RIVERA CHÁVEZ

Director de tesis: Dr. Pablo Roberto Pérez Alcázar

CIUDAD UNIVERSITARIA, MÉXICO, D.F., 2004

## JURADO ASIGNADO

| PRESIDENTE:                  | Dr. Esaú Vicente Vivas                                                 |

|------------------------------|------------------------------------------------------------------------|

| VOCAL:                       | Dr. Pablo Roberto Pérez Alcázar                                        |

| SECRETARIO:                  | Ing. Francisco Rodríguez Ramírez                                       |

| 1 <sup>er</sup> . Suplente:  | Dr. Rogelio Alcántara Silva                                            |

| 2°. Suplente:                | Ing. Noe Cruz Marín                                                    |

|                              |                                                                        |

| Sitio donde se desarrolló el | TEMA:                                                                  |

|                              | Instituto de Ingeniería, U. N. A. M.<br>Coordinación de Automatización |

| DIRECTOR DE TESIS:           | Dr. Pablo Roberto Pérez Alcázar                                        |

| -                            |                                                                        |

| SUSTENTANTES:                |                                                                        |

| José Alberto Llavo           | t López Remigio Antonio Rivera Chávez                                  |

|                              |                                                                        |

|                              |                                                                        |

|                              |                                                                        |

Gracias Dios por entregarme una vida llena de felicidad y dicha, por estar siempre presente, por mi familia y por las personas que han dejado algo en mi, por permitirme alcanzar los objetivos que me he propuesto, por darme virtudes para lograrlos, y por darme defectos para vencerme a mi mismo.

A mi país, por darme una identidad, una historia y por permitirme ser heredero de una gran cultura.

A mis Papas, Lourdes y José, por ser ejemplo de amor, de lucha, de trabajo, de fe, de respeto y de constancia. Por regañarme cuando lo necesito y por apoyarme en mis decisiones. Todo lo que soy ahora se los debo a ustedes. Mi gratitud es infinita. Los amo a los dos.

A mi hermano Angel, por ser ejemplo de éxito, producto del trabajo bien hecho, por empujarme a salir adelante, por creer en mi, por escucharme, por la guía que siempre me brindas y sobre todo por ser mi amigo. A mi cuñada Graciela y a mi sobrina Natalia, por hacerme tío y padrino respectivamente, y por formar una gran familia. Dios los bendiga.

A Jazmín Márquez, por ayudarme a ver el mundo diferente; por ser mi alegría, mi mejor equipo y sobre todo, mi amor; por caminar a mi lado cuando más lo he necesitado; por trazar conmigo un camino que llegará muy lejos y por mostrarme a Dios en tu sonrisa y en tus ojos. Gracias por todo Flaca.

A mis cuatro abuelos, por el cariño que recibí y que recibo de ellos todos los días.

A mi padrino Arturo López, a mi Abuelo Antonio López y a mi tía Yolanda Llavot. Por el cariño que me brindaron cuando aun estaban con nosotros, y por permitirme aprender tantas cosas de ustedes.

Siempre estarán en mi corazón.

A mis tíos Paty y Raymundo; por ayudarme a crecer, por apoyarme siempre y por su cariño incondicional.

A todos mis tíos, por su cariño y apoyo, y a mis primos; sean fuertes chavos... Si se puede!!!

A Misael Guzmán, Leonardo Cabrera, Francisco Galindo, Adriana Gudiño, Marco A. Olguín, y Claudia Olvera, por todos estos años de amistad; por todas las experiencias vividas y las que aun nos quedan; por encontrarlos siempre en mi camino a pesar de la distancia. Gracias.

A Francisco J. Torner y a Heriberto Pérez; por su amistad y su paciencia; por escucharme y apoyarme siempre; por jalarme las orejas y por reír conmigo. Gracias.

A Ian G. Monsivais, "The hero of the day".

A Remigio, por ser un buen equipo durante la escuela, por el apoyo que me has brindado tanto profesional como personalmente. Tu amistad ha sido una de las mejores experiencias de la Universidad. Gracias.

A la que algún día será mi esposa y a mis futuros hijos.

JOSÉ ALBERTO LLAVOT LÓPEZ.

A mis padres, Remigio y María de la Luz, por ser apoyo y estímulo constante en mi diario caminar, gracias por todo lo que me han otorgado a lo largo de mi vida; por ser luz y fuerza en aquellos momentos mas difíciles, por ser los mejores padres que hubiera podido tener y por enseñarme el camino correcto para convertirme en un buen ser humano....

A mi hermano Rodrigo, por ser más que un confidente y amigo para mi, por el tiempo y los momentos que hemos compartido juntos, por tenerme paciencia y cariño y por la confianza que ha depositado en mi persona al creer en mi sin dudar jamás....

A mi novia Ana Rosa, por aparecer como una centella de luz en esos momentos donde la oscuridad me rodeaba por completo, por darle un rumbo y sentido fijo a mi vida; nunca olvides guardada esa sonrisa que tanto me ha enamorado desde el momento en el que te conocí. Te amo como solo se puede amar una sola vez en la vida y ansío cumplir sueños y anhelos a tu lado...

A mi abuelita Paula, por cuidar de mi cuando era un niño y por ayudar en mi formación como ser humano. Gracias por darme un poco de su tiempo y sabiduría abuelita, así como de todos aquellos regaños que me hicieron aprender de la vida, mil gracias.

A mi familia entera, incluyendo a las familia Rivera y a la familia Chávez, por compartir vivencias juntos y por el tiempo compartido en cada oportunidad que se ha presentado.

A todos mis profesores desde la educación preescolar hasta la educación profesional por ser participes en mi formación, gracias por todos los conocimientos entregados hacia mi persona, por su valiosa colaboración en mi formación estudiantil; porque ustedes me han llevado hasta donde me encuentro actualmente.

A todos mis compañeros de clase que he tenido, por las experiencias compartidas y el tiempo transcurrido en el aula. Especialmente a mi compañero de tesis José Alberto Llavot, por representar la amistad en su máxima expresión y apoyarme cuando lo he necesitado.

#### REMIGIO ANTONIO RIVERA CHÁVEZ

#### AGRADECIMIENTOS

A la Universidad Nacional Autónoma de México, por todo lo que nos ha brindado sin pedirnos nada a cambio, por los conocimientos y cultura que han hecho de nosotros mejores personas.

Al Instituto de Ingeniería, en especial a la Coordinación de Automatización, por permitirnos desarrollar este proyecto de tesis dentro de sus instalaciones, y por el apoyo brindado dentro de la duración del mismo.

Al Doctor Pablo Roberto Pérez A., por la paciencia, enseñanza, apoyo y amistad ofrecidas durante este trabajo. Reciba nuestra infinita admiración y agradecimiento.

Al CONACyT por el apoyo económico brindado para la realización de este proyecto.

A los sinodales Dr. Esaú Vicente, Ing. Francisco Rodríguez, Dr. Rogelio Alcántara e Ing. Noe Cruz por su colaboración en la mejora de este trabajo.

#### **RESUMEN**

En el ámbito del procesamiento digital de señales existen distintas alternativas de muestreo, por lo que es finalidad de esta tesis el dar un panorama general de lo que significa el muestreo pasobanda de señales; con la finalidad de preparar su aplicación posterior a equipos ingeniería biomédica como son los de resonancia magnética nuclear o ultrasonido. Para lograr esto, se propone una configuración alternativa para el receptor de un equipo de resonancia magnética nuclear, utilizando el submuestreo y un receptor digital.

Se presentan los aspectos teóricos que sirvieron como base para el desarrollo de este trabajo, incluyendo: tipos de muestreo, decimación, cuantificación, conversores A/D, zFFT y detección en cuadratura.

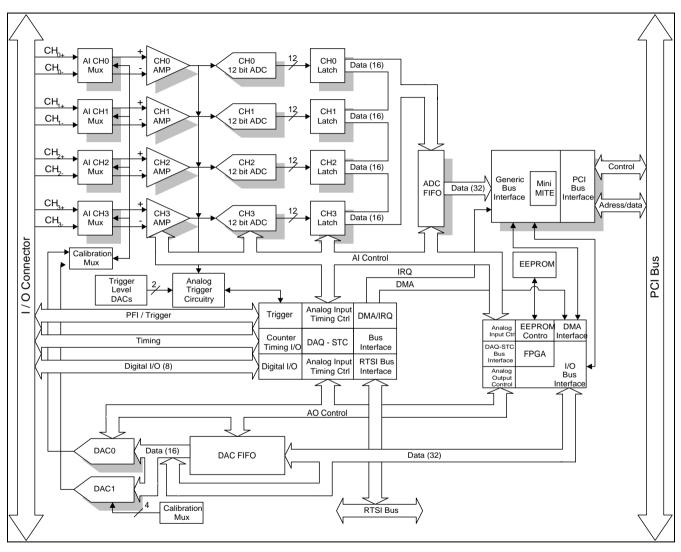

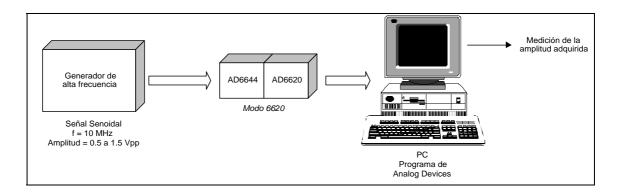

Dentro del aspecto práctico de la tesis, se proponen dos sistemas de adquisición de señales pasobanda distintos, que emplean técnicas de submuestreo, uno constituido a partir de una tarjeta comercial de adquisición de datos (NI PCI-6110) junto con un adaptador de ancho de banda y otro constituido por el conversor AD6644 y el receptor digital AD6620. Se muestra el diseño y calibración del circuito adaptador de ancho de banda, necesario para el manejo de señales pasobanda de alta frecuencia, además de que se describen las características de los dos sistemas de adquisición, el software de control desarrollado para cada uno y se evalúan los resultados obtenidos mediante cada método.

Finalmente en base a los resultados obtenidos, se concluye la viabilidad de ambas alternativas y se indican las ventajas y desventajas encontradas en estos sistemas.

# ÍNDICE

| RESUMEN                                                                       | I  |

|-------------------------------------------------------------------------------|----|

|                                                                               |    |

| ÍNDICE                                                                        | 1  |

| 1. INTRODUCCIÓN                                                               | 5  |

| 1.1. Trabajo previo y aplicaciones del submuestreo                            |    |

| 1.2. Objetivos                                                                |    |

| 1.3. Estructura de la tesis                                                   |    |

| 2. ASPECTOS TEÓRICOS                                                          | 15 |

| 2.1. Muestreo                                                                 | 15 |

| 2.1.1. Teorema del muestreo o Teorema de Nyquist                              | 16 |

| 2.1.2. Aliasing o solapamiento espectral.                                     | 19 |

| 2.1.3. Muestreo con pulsos de duración finita                                 | 21 |

| 2.1.4. Muestreo pasobanda                                                     | 24 |

| 2.2. MODIFICACIÓN DE LA FRECUENCIA DE MUESTREO                                | 26 |

| 2.2.1. Decimación                                                             | 28 |

| 2.2.2. Decimación aplicada a la conversión A/D: Simplificación de los filtros |    |

| antialiasing.                                                                 | 30 |

| 2.3. Cuantificación                                                           | 32 |

| 2.3.1. Aproximación a la teoría de la cuantificación                          | 32 |

| 2.3.2. Ruido de cuantificación                                                | 34 |

| 2.3.3. Efectos de la decimación sobre el ruido de cuantificación              | 35 |

| 2.4. Conversores A/D                                                          | 36 |

| 2.4.1. Conversores A/D de alta velocidad                                      | 38 |

| a) Conversores Flash o conversor A/D de comparador en paralelo                | 40 |

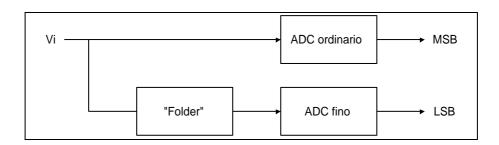

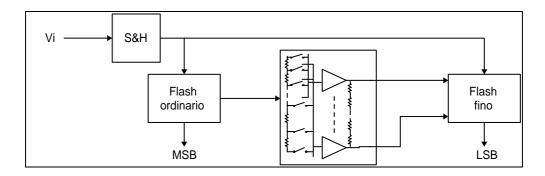

| b) Conversores A/D de Doblaje (Folding) e interpolación (Interpoling)         | 41 |

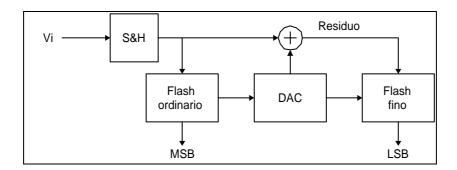

| c) Conversores A/D de dos Pasos (Two Step) y de Subrango (Subranging)         | 41 |

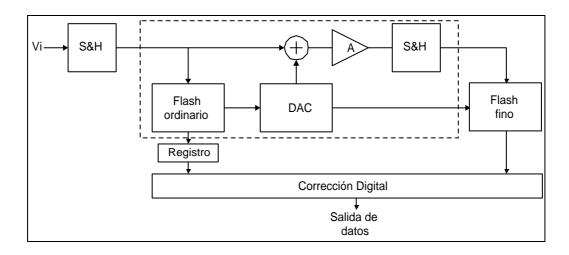

| d) Conversores Pipeline                                                       | 43 |

| 2.4.2. Circuito de Muestreo y Retención (Sample and Hold)                     | 45 |

| 2.5. PROCESAMIENTO DE SEÑALES.                                                 | 46   |

|--------------------------------------------------------------------------------|------|

| 2.5.1. La Transformada Rápida de Fourier y la zFFT                             | 47   |

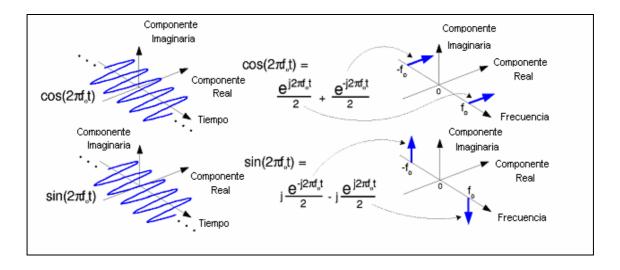

| 2.5.2. Señales en cuadratura                                                   | 50   |

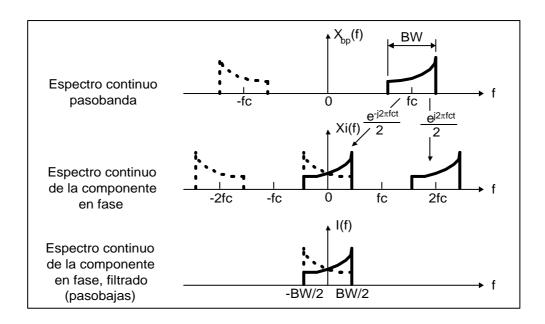

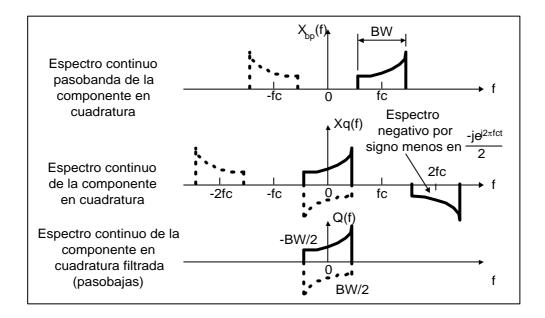

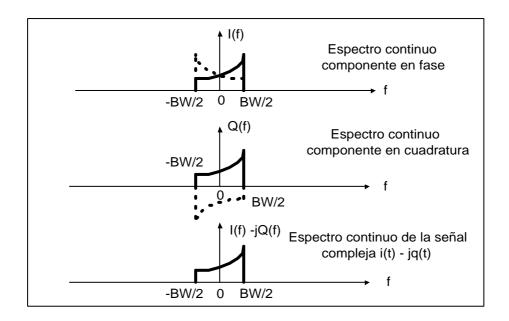

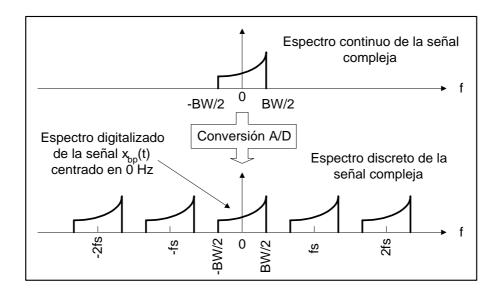

| a) Representación de señales en cuadratura en el dominio de la frecuencia      | 51   |

| b) Señales cuadratura pasobanda en el dominio de la frecuencia                 | 52   |

| 3. EQUIPO Y MÉTODO DE TRABAJO                                                  | 57   |

| 3.1. CARACTERIZACIÓN Y CALIBRACIÓN DEL SISTEMA ADAPTADOR DE ANCHO DE           |      |

| BANDA – DISPOSITIVO DE ADQUISICIÓN NI PCI-6110                                 | 57   |

| 3.1.1. Descripción del dispositivo muti-funcional de adquisición de datos NI I | PCI- |

| 6110                                                                           | 57   |

| 3.1.2. Especificaciones                                                        | 59   |

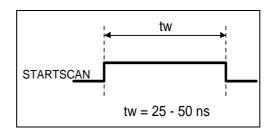

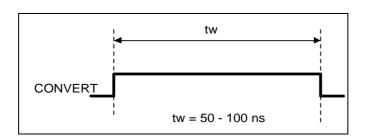

| 3.1.3. Entradas de función programables (PFI's) y señales internas             | 60   |

| 3.1.4. Justificación del uso.                                                  | 63   |

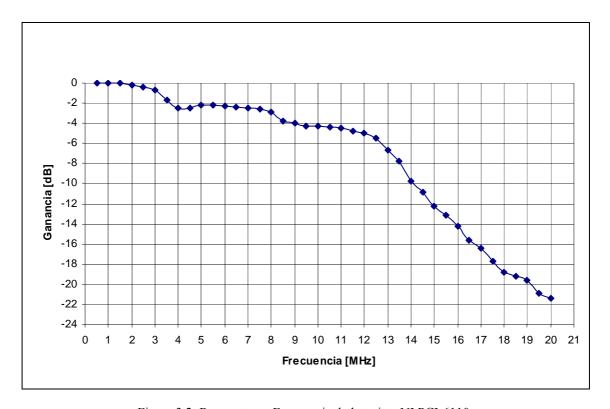

| 3.1.5. Caracterización del Circuito Adaptador de Ancho de Banda (AAB)          | 65   |

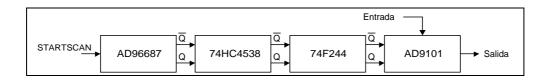

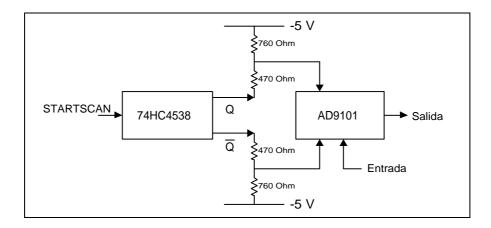

| 3.1.6. Señales de entrada al comparador para generar $CLK / \overline{CLK}$    | 71   |

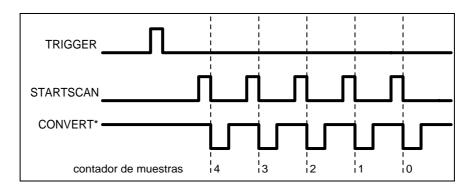

| a) Prueba de calibración 1: STARTSCAN al comparador AD96687,                   |      |

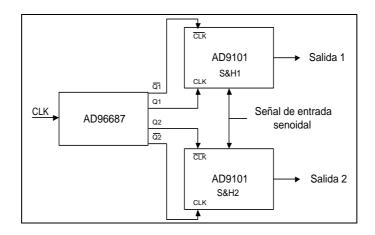

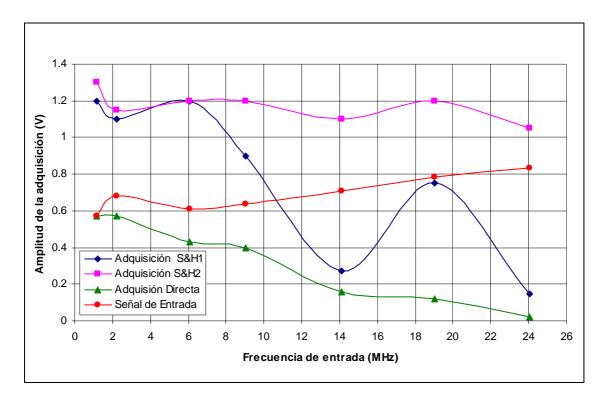

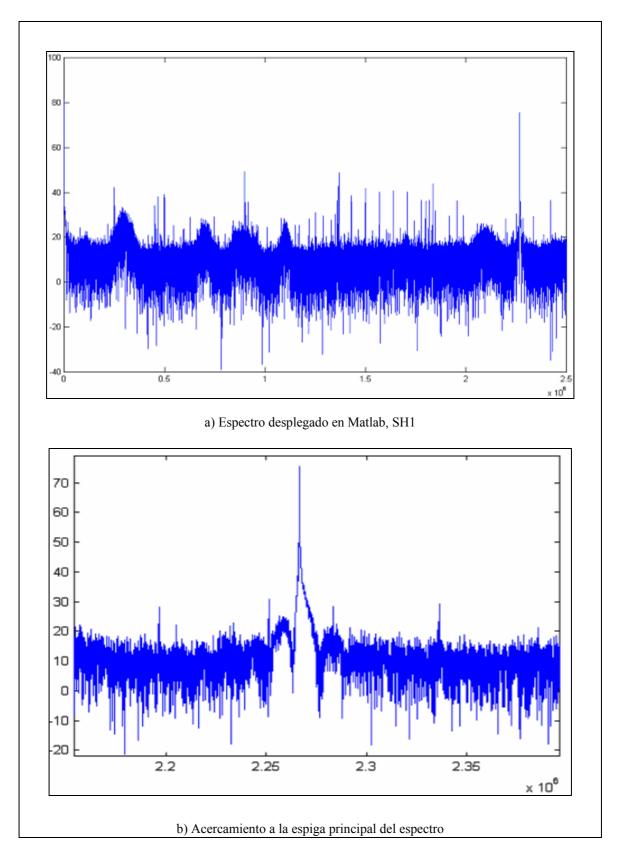

| muestreando una señal senoidal en el SH1 y el SH2                              | 72   |

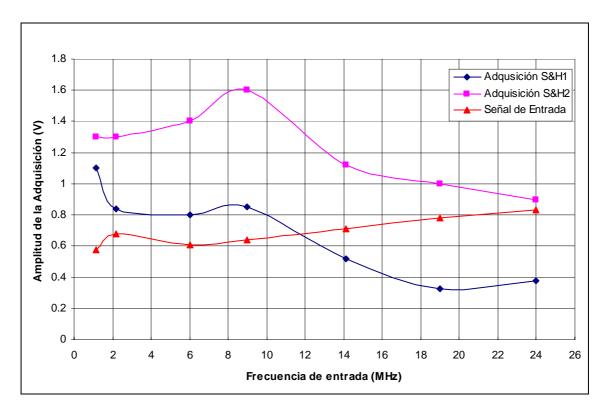

| b) Prueba de calibración 2: CONVERT al comparador AD96687, muestrear           | ıdo  |

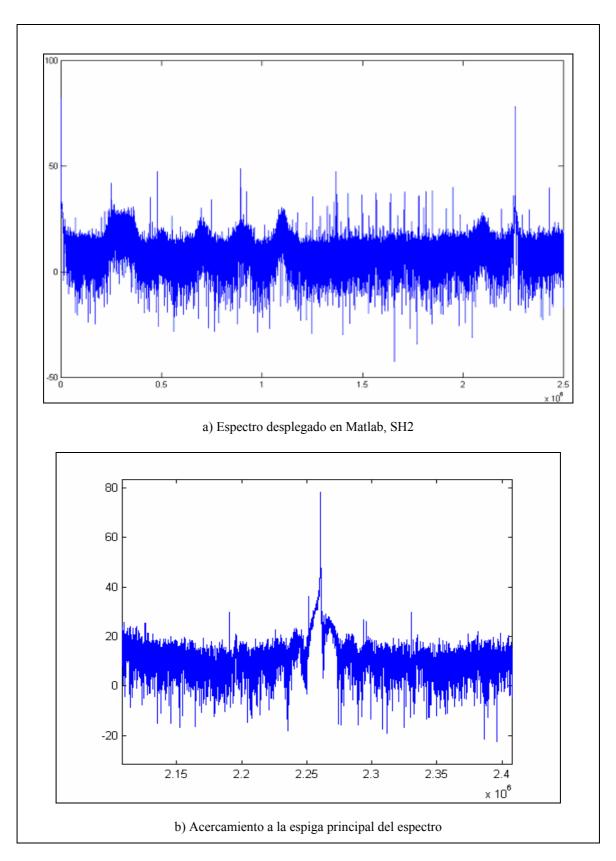

| una señal senoidal en el SH1 y el SH2                                          | 74   |

| c) Conclusión                                                                  | 76   |

| 3.1.7. Pruebas manipulando el STARTSCAN y respuesta en frecuencia del          |      |

| sistema                                                                        | 76   |

| 3.1.8. Características eléctricas del AAB                                      | 83   |

| 3.2 CARACTERIZACIÓN Y CALIBRACIÓN DEL SISTEMA AD6644 – AD6620                  | 84   |

| 3.2.1. Caracterización del Conversor Analógico / Digital AD6644                | 84   |

| 3.2.2. Caracterización del receptor digital de señales AD6620                  | 86   |

| 3.2.3. Modos de operación propios del AD6644 para transmisión de datos al      |      |

| AD6620                                                                         | 91   |

| a) Modo de operación 6620                                                      | 91   |

| b) Modo de operación en bypass                                                 | 92   |

| 3.2.4. Calibración del sistema AD6644 – AD6620                                 | 92   |

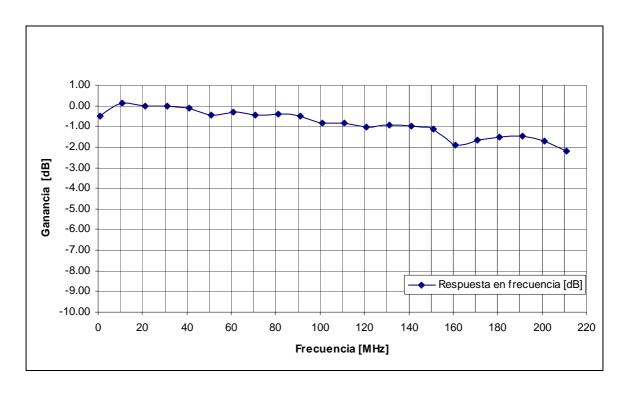

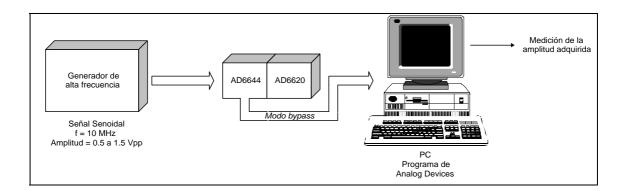

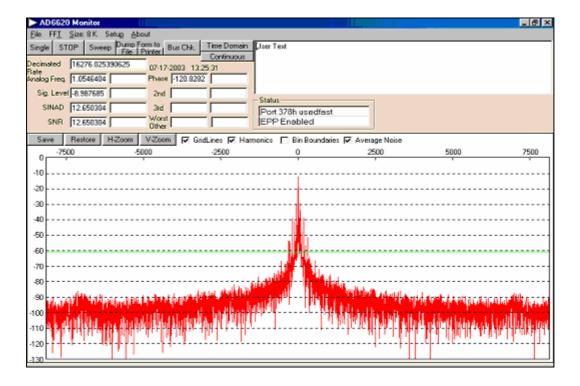

| a) Respuesta en frecuencia                                                     | 92   |

| b) Calibración de amplitud                                                     | 94   |

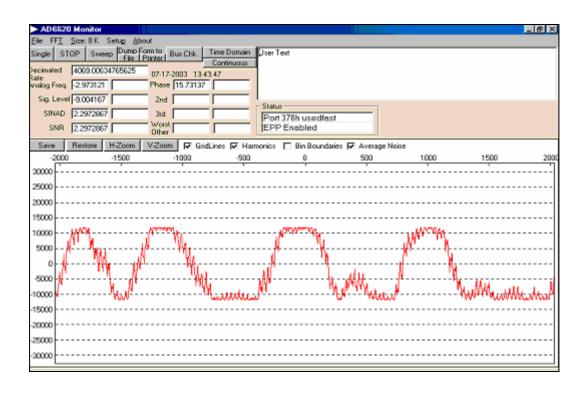

| c) Decimación                                                       | 99  |

|---------------------------------------------------------------------|-----|

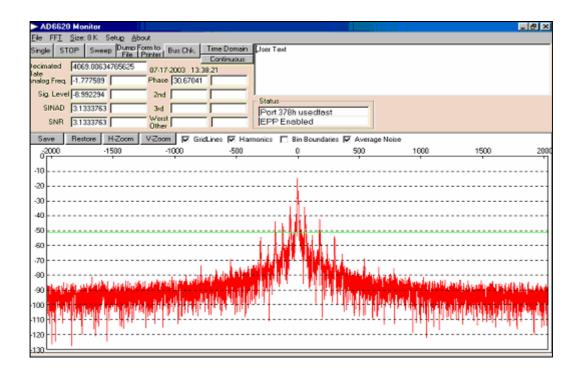

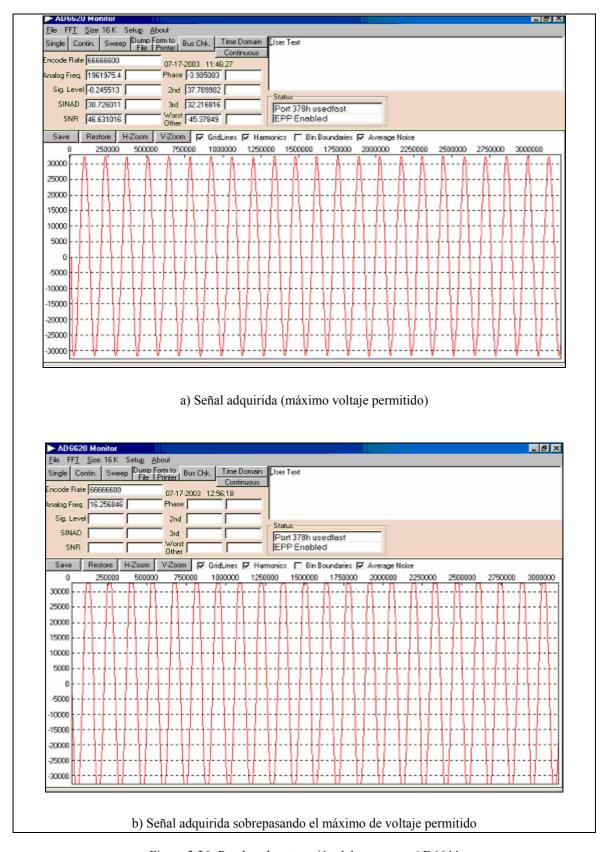

| d) Saturación del conversor AD6644                                  | 105 |

| 3.3. Software de adquisición                                        | 107 |

| 3.3.1. Software de adquisición de LabVIEW                           | 107 |

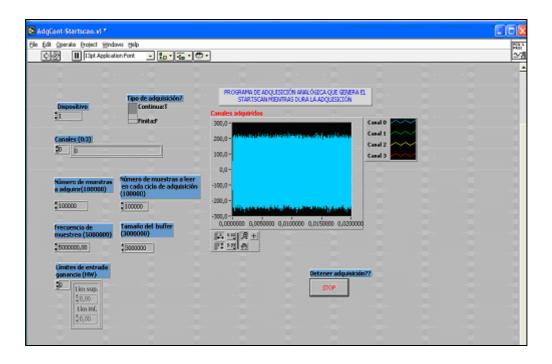

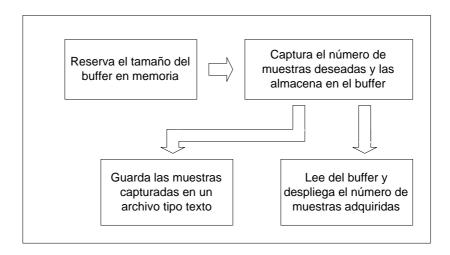

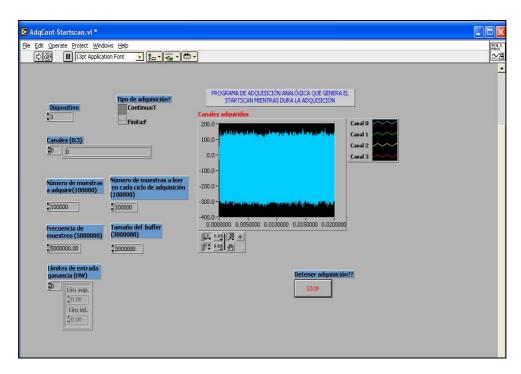

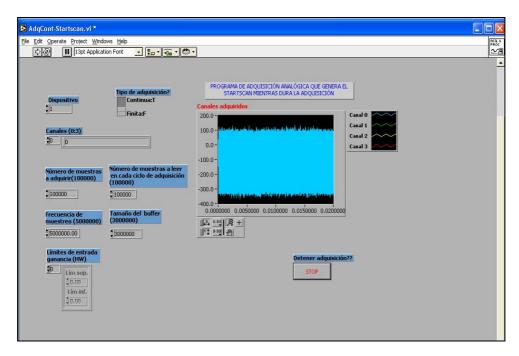

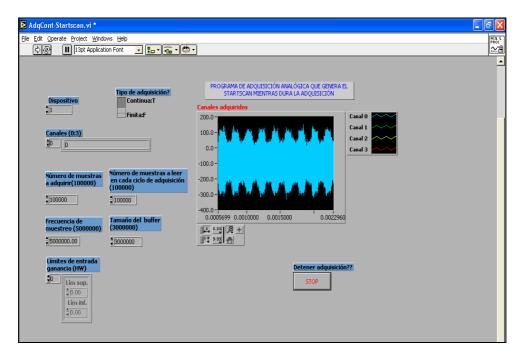

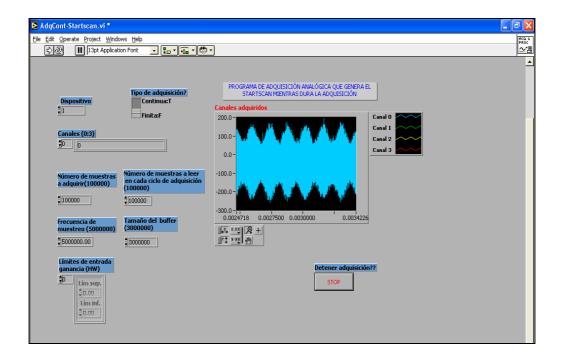

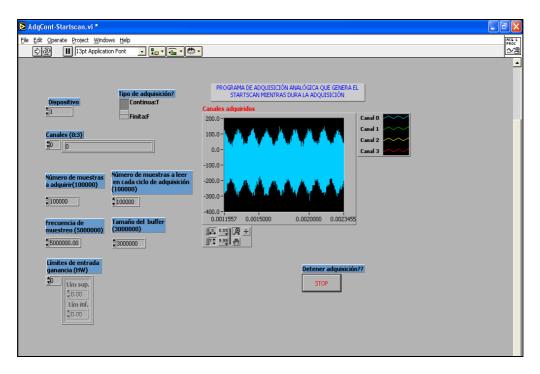

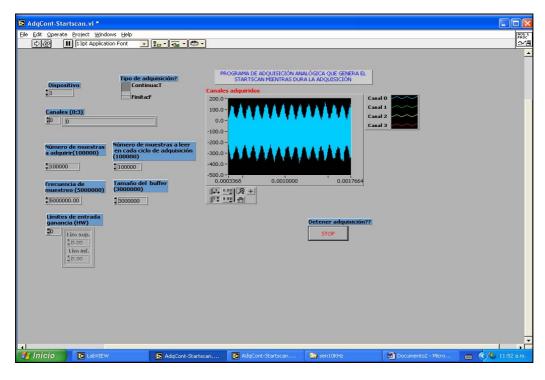

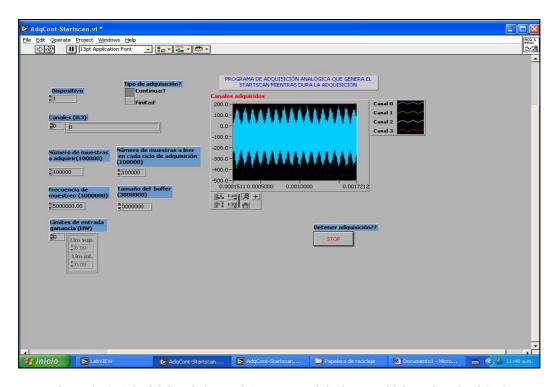

| a) AdqCont-Startscan.vi                                             | 107 |

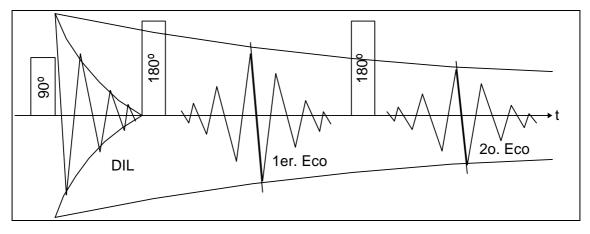

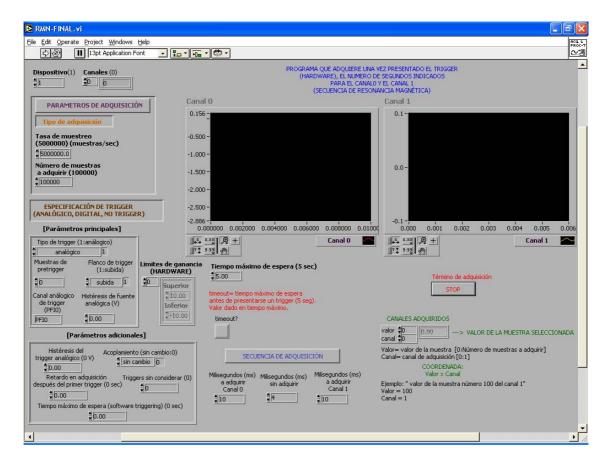

| b) Software de adquisición para señales de Resonancia Magnética     | 111 |

| 3.3.2. Software de adquisición de Analog Devices                    | 117 |

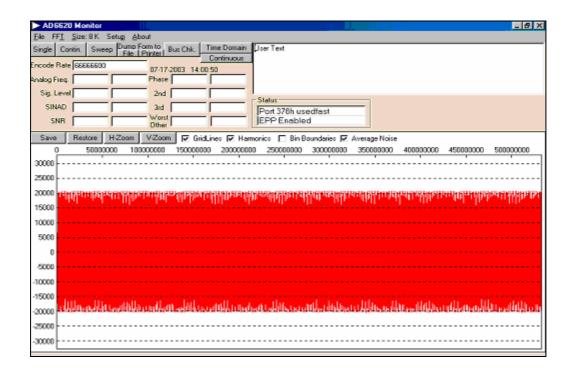

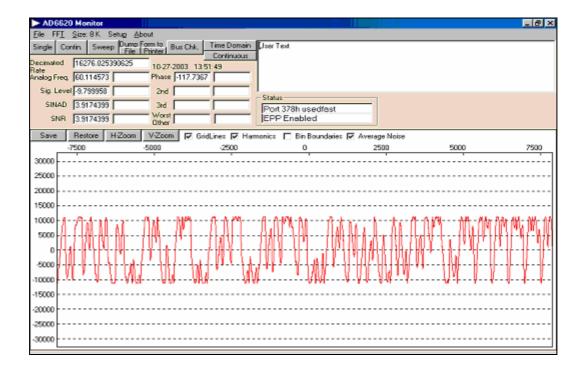

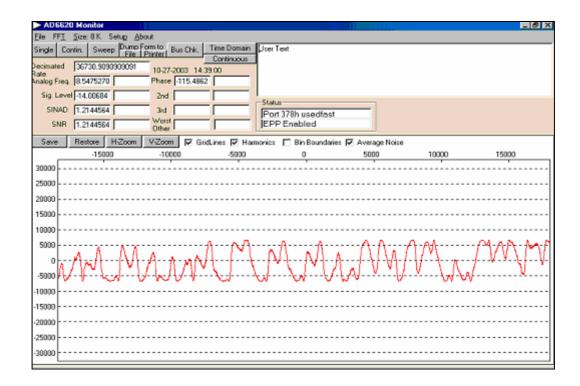

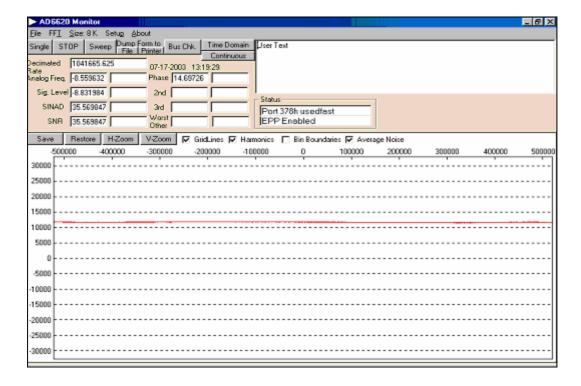

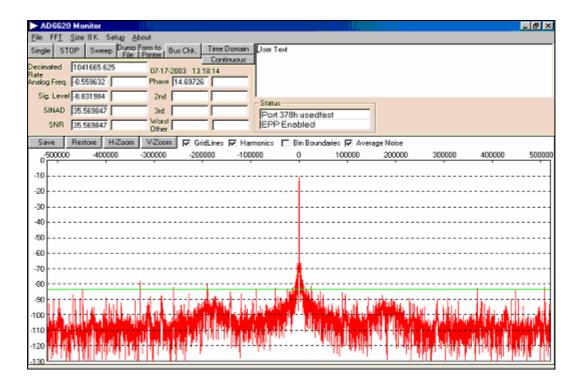

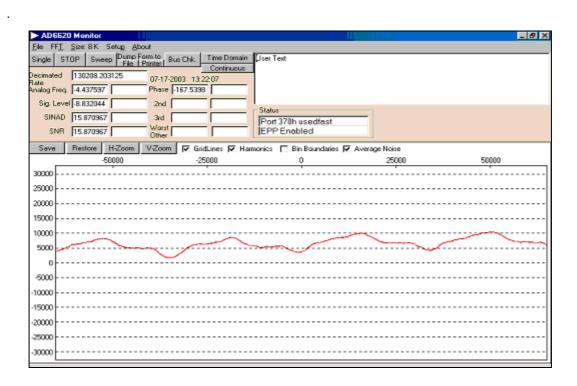

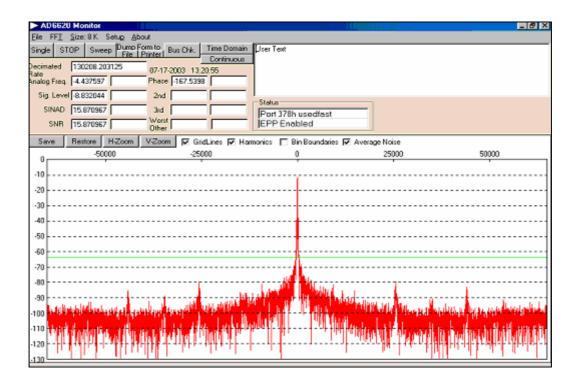

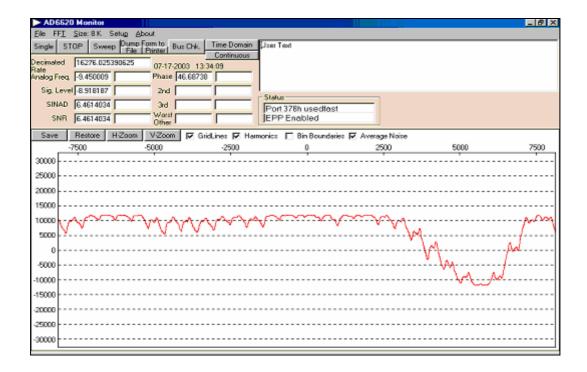

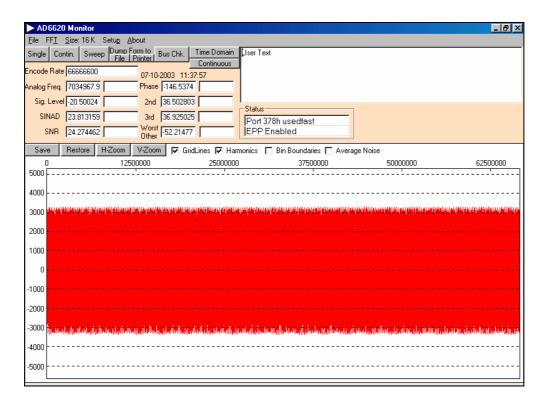

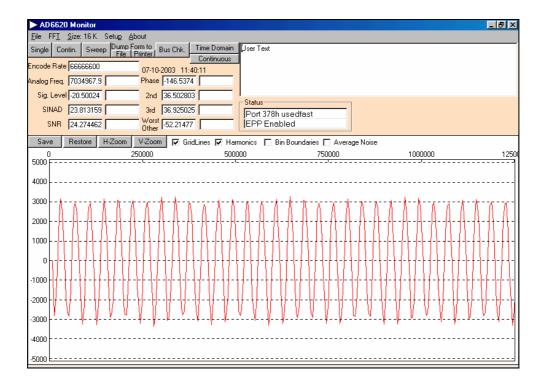

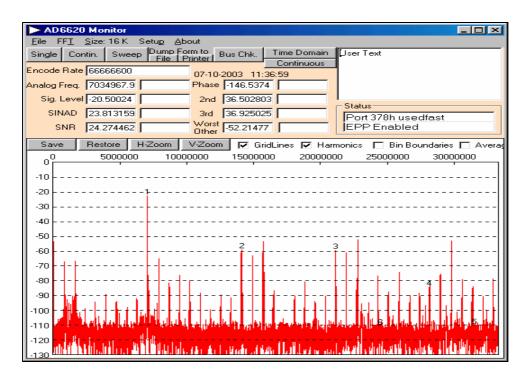

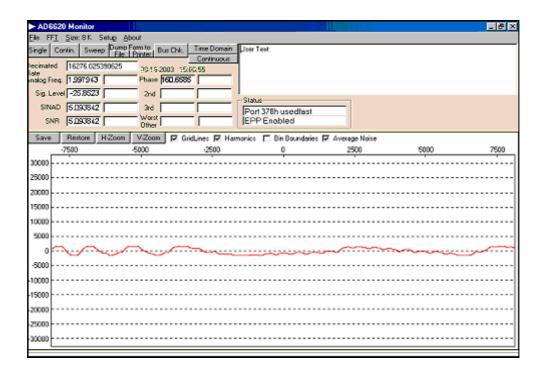

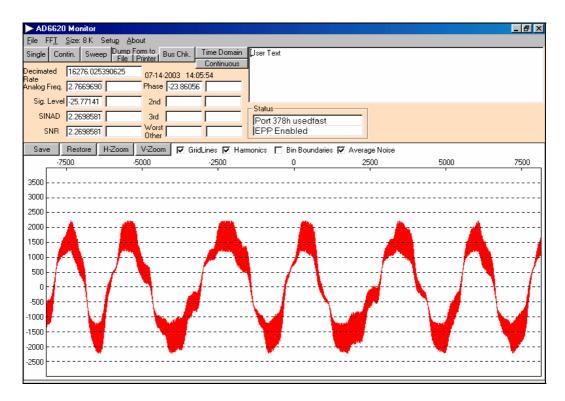

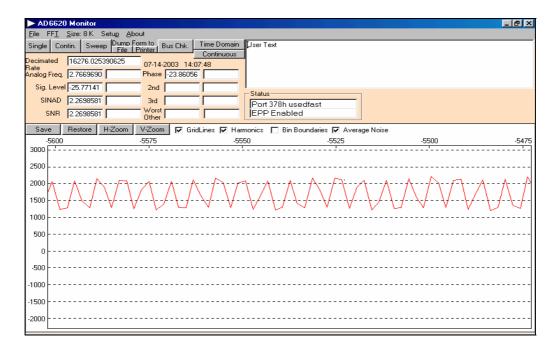

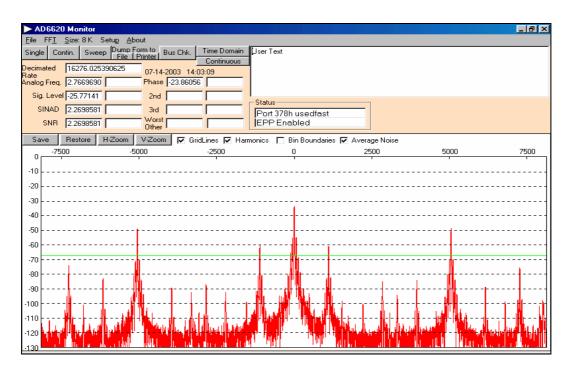

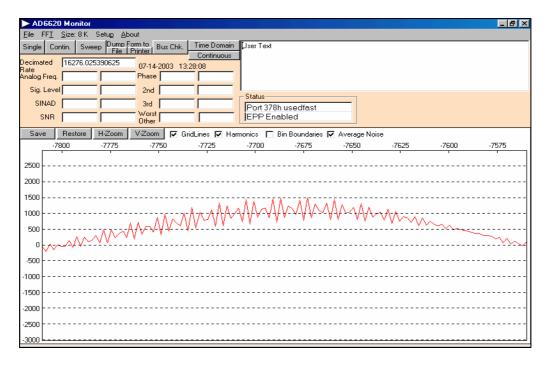

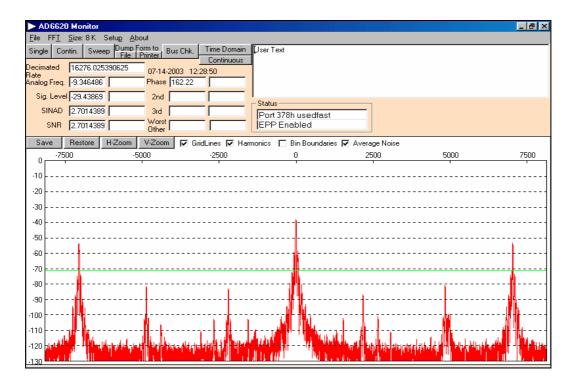

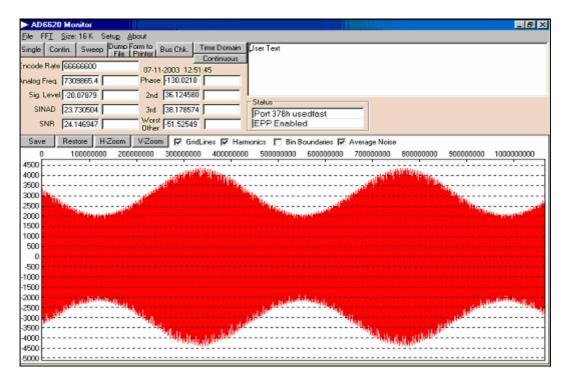

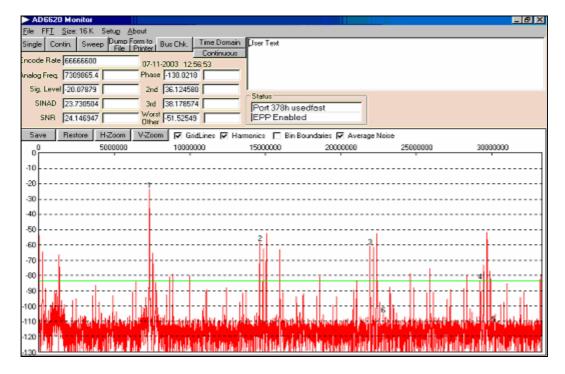

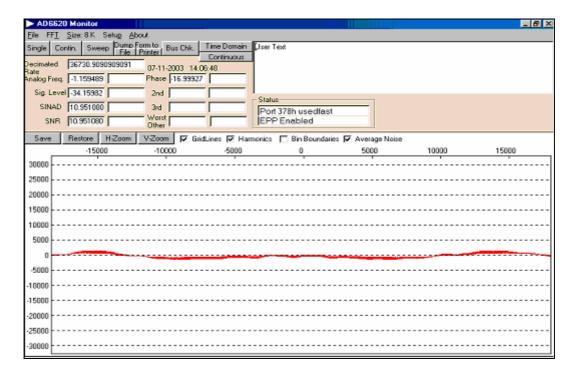

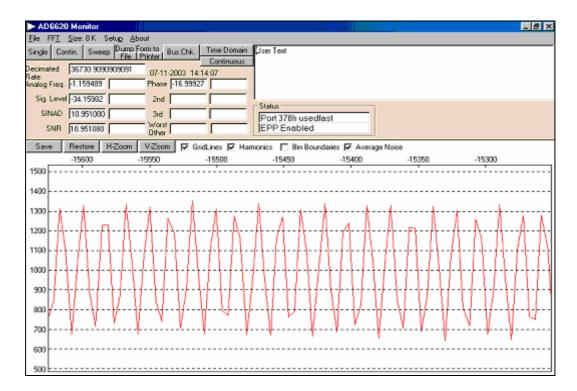

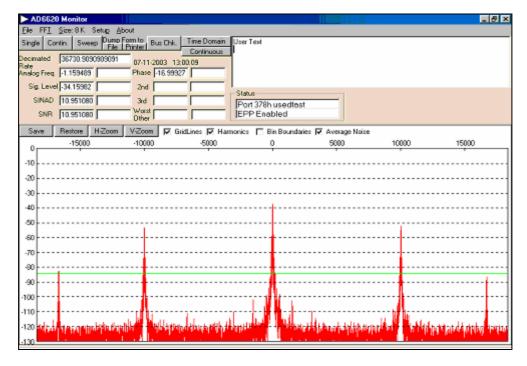

| a) AD6620 Monitor Program                                           | 117 |

| b) AD6620 Controller Program                                        | 120 |

| 4. RESULTADOS EXPERIMENTALES                                        | 123 |

| 4.1. TIPOS DE EXPERIMENTOS REALIZADOS                               | 124 |

| 4.2. Traslado en frecuencia de una señal portadora                  | 124 |

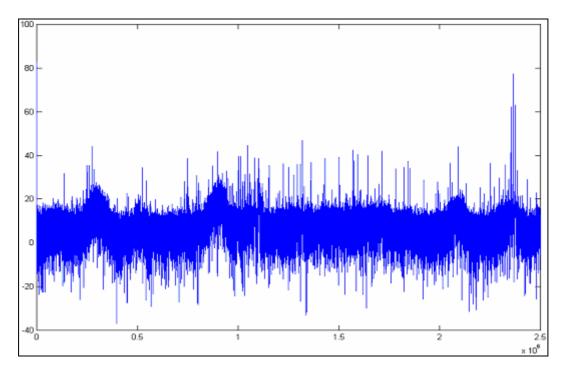

| 4.2.1. Sistema AAB – NI PCI-6110                                    | 125 |

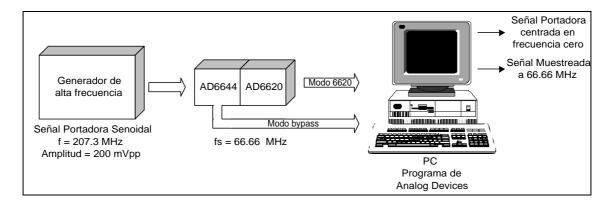

| 4.2.2. Sistema AD6644 – AD6620                                      | 130 |

| a) Adquisición en modo bypass                                       | 131 |

| b) Adquisición en modo 6620                                         | 133 |

| 4.3. Traslado en frecuencia de una señal portadora modulada por una |     |

| SEÑAL CUADRADA                                                      | 137 |

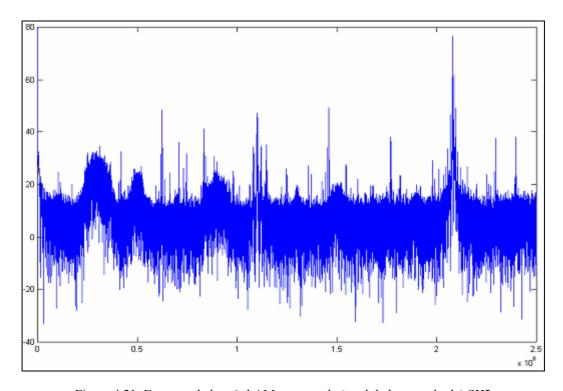

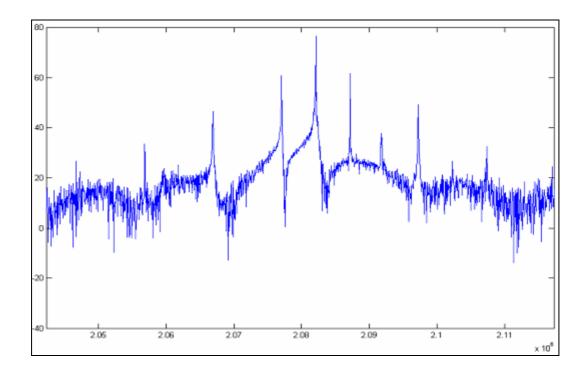

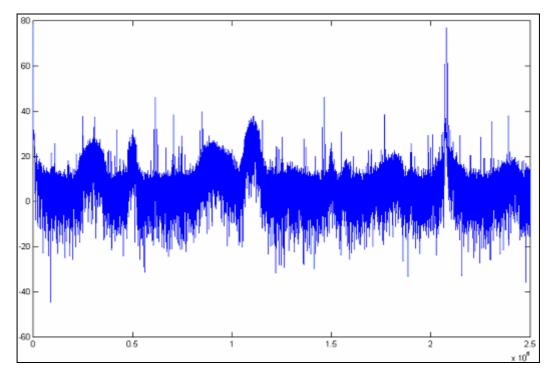

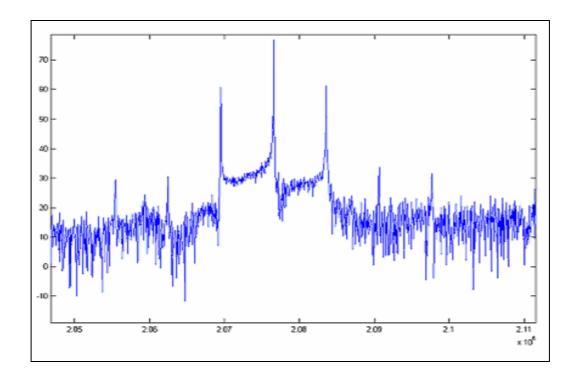

| 4.3.1 Sistema AAB – NI PCI-6110                                     | 138 |

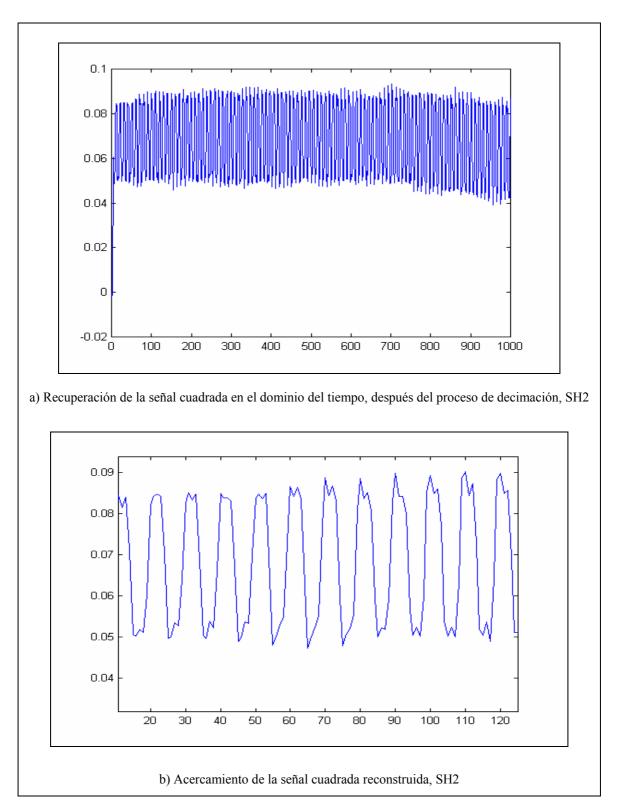

| 4.3.2. Proceso de detección de la señal moduladora                  | 142 |

| 4.3.3. Sistema AD6644 – AD6620                                      | 149 |

| a) Adquisición en modo bypass                                       | 151 |

| b) Adquisición en modo 6620                                         | 152 |

| 4.4. Traslado en frecuencia de una señal portadora modulada por una |     |

| SEÑAL TRIANGULAR                                                    | 156 |

| 4.4.1. Sistema AAB – NI PCI-6110                                    | 157 |

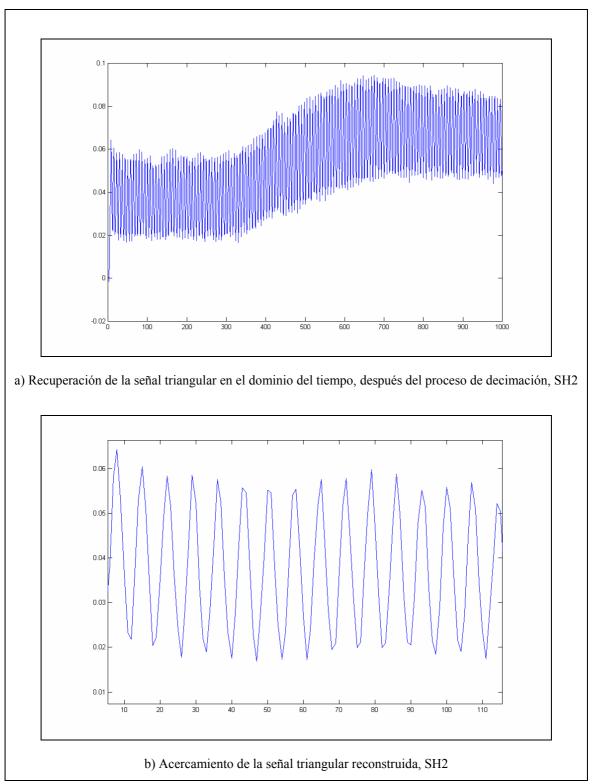

| 4.4.2. Sistema AD6644 – AD6620.                                     | 166 |

| a) Adquisición en modo bypass                                       | 166 |

| b) Adquisición en modo 6620                                         | 168 |

| 4.5 Traslado en frecuencia de una señal portadora modulada por una  |     |

| SEÑAL SENOIDAL.                                                     | 172 |

| 4.5.1. Sistema ABB – NI PCI-6110                                    | 172 |

| 4.5.2. Sistema AD6644 – AD6620                                   | 181 |

|------------------------------------------------------------------|-----|

| a) Adquisición en modo bypass                                    | 181 |

| b) Adquisición en modo 6620                                      | 183 |

| 5. CONCLUSIONES                                                  | 187 |

| ANEXO A: Muestreo uniforme ideal                                 | 191 |

| ANEXO B: Especificaciones de los conversores A/D                 | 193 |

| ANEXO C: Especificaciones de un circuito de muestreo y retención | 197 |

| BIBLIOGRAFÍA                                                     | 199 |

#### 1. INTRODUCCIÓN

Dos de las herramientas más útiles con las que cuenta la medicina actual para la detección de enfermedades son, sin duda, la Resonancia Magnética Nuclear (RMN) y el Ultrasonido. Estas técnicas poseen la ventaja de aportar una gran cantidad de información sobre el estado del paciente sin causarle ningún daño (son técnicas no invasivas), explicando esto, la enorme popularidad con la que gozan no solo dentro del mundo de la salud, sino en diferentes ramas científicas tales como la biología, la química, la ciencia de materiales, entre otras.

Las señales generadas en los equipos de RMN y ultrasonido, son típicas señales pasobanda, a las que se les realiza un procesamiento mediante circuitos analógicos y solo después de ser llevadas a banda base, son convertidas en señales digitales para su posterior análisis numérico. El empleo de técnicas y circuitos digitales proporciona ventajas como la reducción de tamaño y complejidad, estabilidad y mayor versatilidad proporcionada por el uso de la programación. Estos motivos hacen que las técnicas digitales sean muy atractivas en cualquier sistema que emplee procesamiento de señales y como era de esperarse, la RMN y el ultrasonido no podían ser la excepción. Actualmente se esta planteado la aplicación de circuitos digitales en la etapa de procesamiento de estos sistemas, cuando las señales aún se encuentran en el rango de radiofrecuencias. Esta digitalización de los sistemas analógicos ya es ampliamente usada, principalmente, en los sistemas de comunicaciones.

La representación digitalizada de una señal es una versión discreta de dicha señal que, contando con las ventajas descritas anteriormente, pretende ser lo más fidedigna posible a la original. Para poder manipular digitalmente la señal de RMN se requiere la acción de dos procesos: el muestreo y la cuantificación. Del correcto manejo de estos procesos depende la información que contenga la señal digital.

Existen distintas técnicas de muestreo de señales: el muestreo ideal, el muestreo con pulsos de duración finita (uniforme o no uniforme), el muestreo pasobanda, etc. Cada una de ellas presenta ventajas y desventajas durante el proceso de digitalización de las señales, por lo que es necesario seleccionar adecuadamente el tipo de muestreo que se va a utilizar, de acuerdo con las necesidades que se tengan para una determinada aplicación. Las técnicas de muestreo más comunes, como el sobremuestreo y el muestreo Nyquist, son empleadas principalmente para el manejo de señales del tipo pasobajas o señales pasobanda de relativamente baja frecuencia. Sin embargo, el

problema que implica el manejo de señales pasobanda a frecuencias altas requiere de una técnica alternativa, que hasta la fecha, es poco conocida y por consiguiente explotada: el muestreo pasobanda.

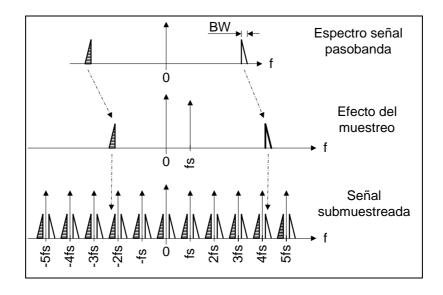

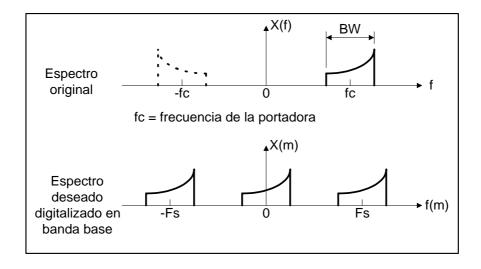

El muestreo pasobanda ( $bandpass\ sampling$ ), también llamado submuestreo (undersampling) o muestreo de frecuencia intermedia ( $IF\ sampling$ ), estudiado desde 1928 y formalizado en la década de los 50s [1], utiliza frecuencias de muestreo menores a dos veces la frecuencia máxima de la señal. El teorema de Nyquist para señales pasobajas establece que una señal debe ser muestreada a tasas mayores que dos veces su frecuencia máxima, de tal manera que se evite el solapamiento espectral o aliasing. Sin embargo, en el submuestreo se aprovecha el hecho de que una señal pasobanda posee la característica principal de ser una señal que en frecuencia no se extiende hasta DC, ya que posee un ancho de banda (BW,  $Band\ Width$ ) definido por la resta existente entre su componente de frecuencia máxima ( $f_M$ ) y su componente de frecuencia mínima ( $f_L$ ), es decir,  $BW = f_M - f_L$ ; por lo que la menor frecuencia de muestreo ( $f_S$ ) a emplear es una función del ancho de banda de la señal, así como de su posición en el espectro. Esto es debido a que los efectos del muestreo provocan que el espectro de una señal pasobanda se repita en los múltiplos enteros de  $f_S$ , cayendo una o varias de sus repeticiones en el ancho de banda de Nyquist, definido entre DC y  $f_S/2$ .

El principal motivo para considerar el uso del submuestreo es el deseo de reducir los requerimientos de velocidad de la sección digital de cualquier sistema. Por ejemplo, una señal pasobanda con BW = 50 kHz centrada en 4.975 MHz, de acuerdo con Nyquist, se debe muestrear con una frecuencia de al menos 10 MHz, por lo que la parte digital del sistema deberá capturar las muestras a esta velocidad. Sin embargo, utilizando el submuestreo de una señal pasobanda, únicamente se requiere una frecuencia de muestreo de 100 kHz; además de que, un conversor A/D a 100 kHz necesita menos potencia, se puede construir con una mayor resolución y es mucho más barato que uno de 10 MHz. Actualmente el muestreo pasobanda esta recibiendo un gran impulso en el campo de las radiocomunicaciones, como se verá más adelante, para el procesamiento de señales de frecuencia intermedia (FI), en lo que se conoce como radio programado o *software radio*, [2].

Al ser las señales de RMN y las de ultrasonido del tipo pasobanda, como se mencionó anteriormente, es factible concluir que el submuestreo puede ser aplicado en los procesos de adquisición que estos sistemas realizan.

Buscando enmarcar mejor el trabajo que se ha desarrollado en la presente tesis se ha considerado conveniente presentar de manera muy somera la estructura de la sección de recepción de un equipo de RMN (muy similar a la de ultrasonido), así como los trabajos previos desarrollados con la idea de introducir las técnicas digitales a estos sistemas.

#### 1.1. Trabajo previo y aplicaciones del submuestreo

Un sistema de RMN esta constituido por un imán para la generación del campo principal, un sistema de gradientes para la codificación espacial, un transmisor de radio frecuencia (RF) para la excitación de la muestra, un receptor de RF (todos estos circuitos son analógicos) y un sistema de adquisición de datos. (para mayor información ver referencia bibliográfica [3])

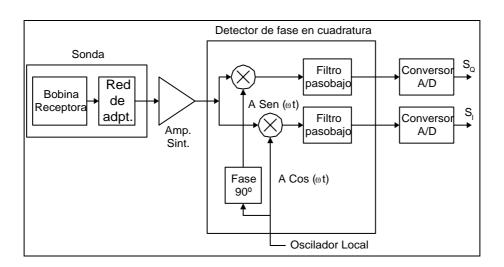

La Figura 1.1 muestra un receptor típico de un equipo de RMN. La sonda, con los amplificadores sintonizados, proporciona una señal centrada en alta frecuencia, con un ancho de banda de algunos kilohertz y amplitud de alrededor de 100 milivolts (mV).

Figura 1.1: Diagrama a bloques simplificado del receptor de un sistema de RMN

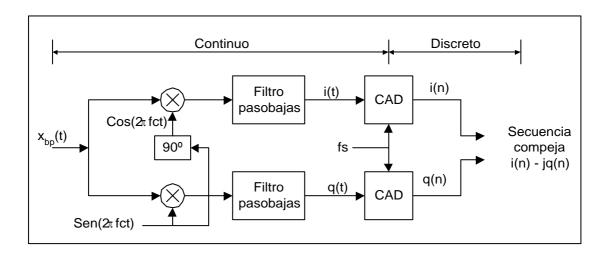

Debido a que hace un par de décadas no se contaba con técnicas digitales capaces de detectar y distinguir entre señales a alta frecuencia, se vio la necesidad de aplicar una técnica que eliminara primero la portadora y después permitiera el procesamiento en banda base. Esta técnica es el proceso de detección de fase simple o en cuadratura, que proporciona la información en la banda requerida o en bajas frecuencias. El problema es que este proceso obliga a trabajar con niveles de señal

relativamente pequeños (100 mV aprox.) con el propósito de evitar la saturación del detector, además de producir pérdidas en la señal y por consiguiente un deterioro en la relación señal a ruido, por lo que se introduce filtrado y amplificación en el canal de salida del detector. Por otro lado, la detección en cuadratura involucra la generación de dos señales de referencia cuya diferencia de fase de 90° debe ser precisa, por lo que se emplean circuitos bastante complejos [4].

Tomando en cuenta la diversidad de problemas que se pueden encontrar en la etapa de recepción, se ha considerado adecuado evaluar la utilización del submuestreo en el procesamiento y en la reconstrucción de imágenes de RMN de tal forma que por este medio se introduzcan las ventajas potenciales del procesamiento digital, reduciendo de esta forma las exigencias propias que el muestreo Nyquist impone.

En un trabajo previo se propuso un sistema de procesamiento de señal de resonancia magnética y de obtención de imágenes basado en la técnica de submuestreo [4], el cual utilizó un osciloscopio digital programable, controlado por una PC a través de un bus GPIB, como sistema de adquisición. A pesar de obtener imágenes de cierta calidad, este sistema contó con varias restricciones impuestas, principalmente, por el uso del osciloscopio y la PC 486 empleada, tales como la baja resolución (8 bits), pequeña longitud de registro, baja velocidad de procesamiento, dificultad para lograr la sincronización entre canales, etc.

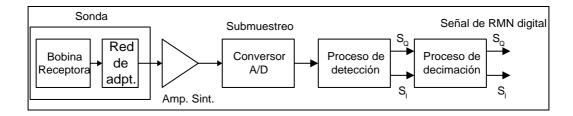

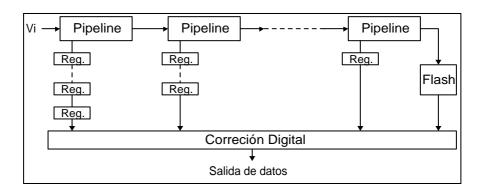

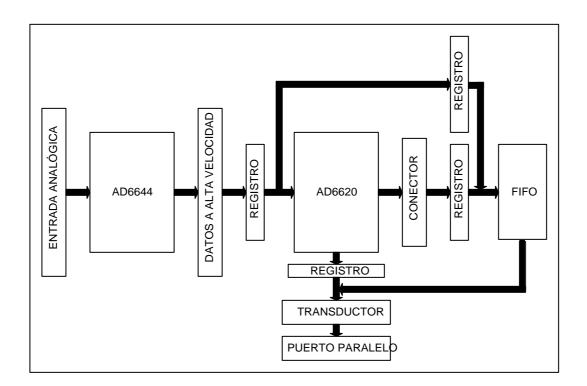

Por motivos como los anteriores, se considera en este trabajo de tesis el uso de un receptor digital directo, como solución al sistema de procesamiento propuesto en el trabajo previamente descrito. Basado en el submuestreo, el receptor digital permite eliminar las etapas analógicas de detección en cuadratura y filtrado pasobajas de los sistemas de resonancia tradicionales como el mostrado en la Figura 1.1. El esquema del receptor propuesto, se muestra en la Figura 1.2.

Figura 1.2: Diagrama de bloques del receptor propuesto para un sistema de RMN

Este receptor es similar al propuesto en [4], con la diferencia de la sustitución del osciloscopio por el receptor digital, además del uso de una computadora de mayor velocidad.

El resultado es teóricamente similar al obtenido utilizando sobremuestreo, pero con varias ventajas, como son: un costo mucho menor y la posibilidad de extender el número de sistemas en los cuales se pueden aplicar las técnicas digitales directamente, aunque con la desventaja de obtener, posiblemente, una relación señal a ruido menor.

En Latinoamérica, el submuestreo ha sido muy poco estudiado. Las limitaciones económicas impuestas a la investigación en dicha región, han dejado que esta técnica solo sea aplicada en países con un alto nivel tecnológico; por lo que la necesidad de estudiar y conocer tanto sus alcances como sus limitaciones resulta inminente como una nueva alternativa en la resolución de problemas de procesamiento.

Para dar una mejor idea de la aplicación actual del submuestreo, se presenta una breve descripción de los receptores digitales que lo utilizan actualmente en el área de comunicaciones.

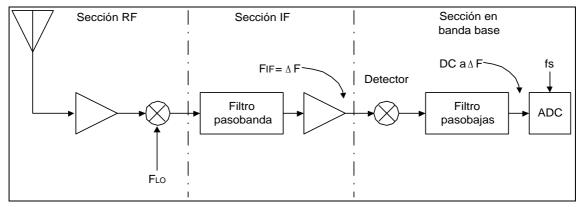

Un diagrama de bloques de un receptor digital tradicional se muestra en la Figura 1.3:

Figura 1.3: Simplificación de un receptor digital usando muestreo en banda base

El mezclador de la sección de radio frecuencia (RF) del receptor multiplica la señal proveniente de la antena con la generada por el oscilador local. La información deseada esta contenida en un pequeño ancho de banda de frecuencias  $\Delta F$ . En los receptores actuales,  $\Delta F$  puede ser tan grande como unos cuantos megahertz. La frecuencia del oscilador local es escogida de tal forma que el ancho de banda de  $\Delta F$  este centrado cerca de la frecuencia intermedia (IF, *Intermediate Frecuency*) a la salida del filtro pasobanda. Algunas frecuencias intermedias populares, varían entre 10 y

100 MHz. Después, el detector entonces traslada la frecuencia  $\Delta F$  hacia banda base, donde es filtrada y procesada por un conversor A/D. Los receptores actuales pueden tener diversas etapas de procesamiento de RF e IF, pero el diagrama propuesto solo ejemplifica los conceptos.

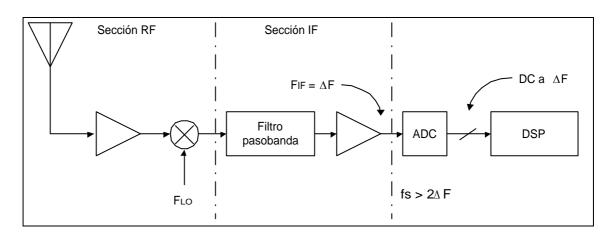

En un receptor que utiliza directamente técnicas de submuestreo (también llamadas de muestreo pasobanda o de muestreo de IF), la señal en IF es aplicada directamente a un conversor analógico digital con un ancho de banda amplio, tal como se muestra en la Figura 1.4. La frecuencia de muestreo del conversor es escogida para ser al menos  $2\Delta F$ . El proceso de muestreo de la IF a la tasa de muestreo apropiada produce que uno de los componentes repetidos de  $\Delta F$  aparezca en el ancho de banda de Nyquist. Algunas técnicas de procesamiento son utilizadas para manipular digitalmente la señal en banda base. Este diseño elimina el detector, además del ruido y la distorsión asociados a él. Existe también una mayor flexibilidad al procesar digitalmente la señal, debido a que la tasa de muestreo del conversor A/D puede ser modificada de tal forma que se localice la posición exacta de la señal  $\Delta F$  ubicada en banda base.

Figura 1.4: Simplificación de un receptor digital usando muestreo pasobanda

El principal problema de este diseño es que el conversor A/D debe ser capaz de digitalizar adecuadamente señales que se encuentran fuera del ancho de banda de Nyquist, rango para el cual están diseñados la mayoría de los conversores. Sin embargo, existe la posibilidad de incrementar el ancho de banda del conversor e incluir así frecuencias mayores correspondientes a señales pasobanda de alta frecuencia.

Aplicaciones como las descritas anteriormente, que utilizan el muestreo pasobanda, generalmente requieren conversores A/D con una baja distorsión para una entrada en una frecuencia intermedia específica.

Otra aplicación del muestreo pasobanda se da en las estaciones de radio celular digital. Para sistemas con frecuencias de RF en 900 MHz, 70 MHz es la frecuencia intermedia más popular. Para sistemas que usan una frecuencia de RF de 1.8 GHz, se utilizan IFs entre 200 y 240 MHz. Estas frecuencias son alcanzables por los conversores A/D que se encuentran actualmente en el mercado como el AD6644 (BW = 300 MHz, a 14 bits) o el AD9432 (BW = 500 MHz, a 12 bits) de Analog Devices, entre otros, [5].

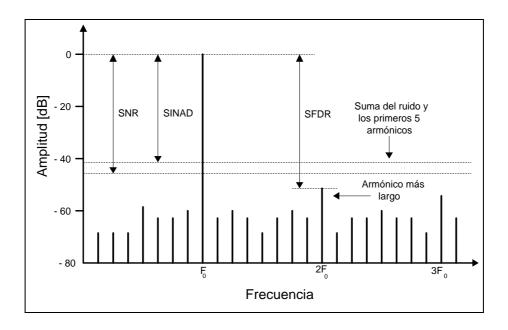

Así, debido a su gran importancia, el procedimiento para seleccionar el conversor A/D a utilizar, en cualquier aplicación que emplee técnicas de submuestreo, debe ser realizado con cuidado, teniendo en cuenta el ancho de banda de la señal de interés, así como su localización en frecuencia. El ancho de banda de la señal determina la mínima frecuencia de muestreo necesaria, sin embargo, para simplificar los requerimientos del filtro antialising utilizado para recuperar la señal original, una tasa de muestreo mayor a 2.5 veces el ancho de banda de la señal es apropiada [5]. Después de determinar la frecuencia de muestreo aproximada, se debe seleccionar el conversor de acuerdo con los valores deseados del rango dinámico libre de armónicos (SFDR, Spurious Free Dynamic Range) y de la relación señal a ruido (SNR, Signal to Noise Ratio) entregados por el conversor en la IF de interés. Es en este punto donde ocurre un dilema pues, por lo regular, encontramos que los conversores A/D, por ejemplo, de 10 megamuestras por segundo (MSPS, Mega-Samples per Second) no poseen un valor adecuado de SNR y SFDR para el valor de IF necesario, a pesar de que su comportamiento sea excelente en frecuencias bajas. Para cumplir con estas características, generalmente se necesita un conversor A/D con una frecuencia de muestreo mucho mayor que la que se requiere normalmente.

De acuerdo con estos criterios, la selección del conversor A/D que nos permita realizar el muestreo de señales pasobanda mediante técnicas de submuestreo, no es una decisión arbitraria, más bien, corresponde a una difícil decisión dentro de la amplia variedad de características encontradas en los distintos tipos de conversores.

En la actualidad, las distintas arquitecturas que presentan los conversores A/D comerciales, nos permiten elegir entre varias alternativas para el procesamiento de señales pasobanda (como se verá en el capítulo 3). Por ejemplo, los conversores A/D sigma-delta tradicionales contienen integradores, los cuáles actúan como filtros pasobajas. Poseen anchos de banda de entrada analógicos que se extienden desde DC, y el ruido de cuantificación es expulsado hacia frecuencias mayores que no son de interés.

Sin embargo, su diseño e implementación es costoso y no existe aún acuerdo universal sobre sus características ideales

De igual manera, encontramos en el mercado conversores A/D de aproximaciones sucesivas, usados en bajas frecuencias; conversores *flash*, también llamados en paralelo y cuya principal ventaja es su alta velocidad; conversores *Ripple* o serie, que emplean un bit por etapa, y conversores de subrango *pipeline*<sup>1</sup> que emplean subsistemas de conversores flash logrando así una mayor resolución que si estos últimos se encontraran solos. [6]

Debido a las oportunidades que los conversores A/D ofrecen, el procesamiento de señales pasobanda puede llevarse a cabo de múltiples formas dependiendo de las necesidades que se quieran cubrir. En nuestro caso, para obtener señales pasobanda de RMN empleando submuestreo, se consideraron dos alternativas:

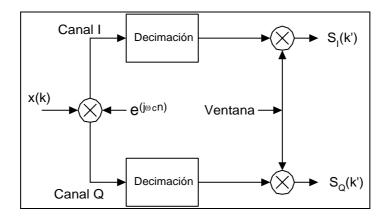

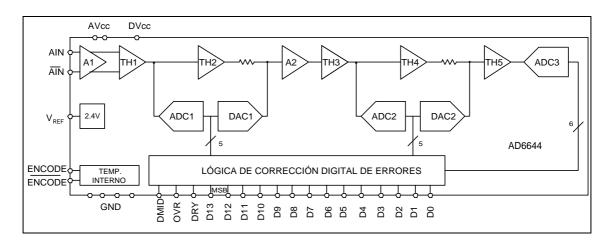

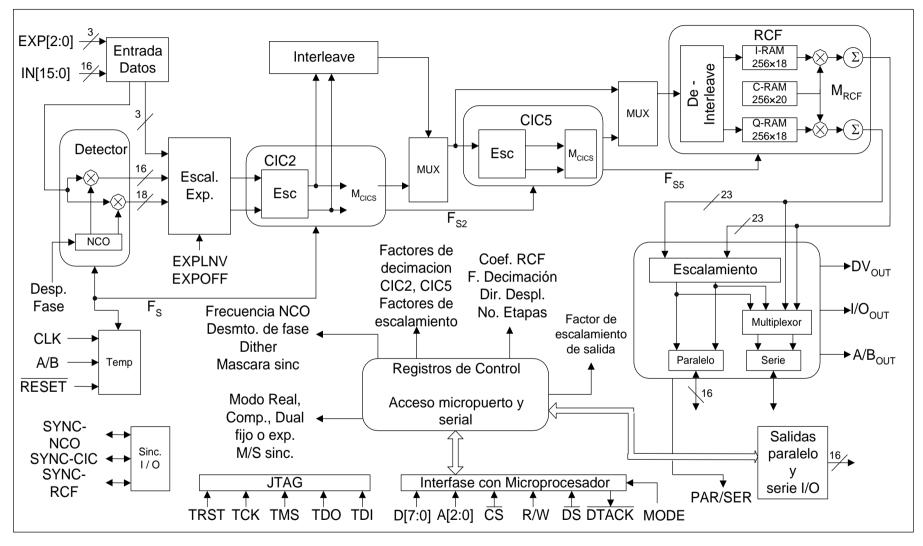

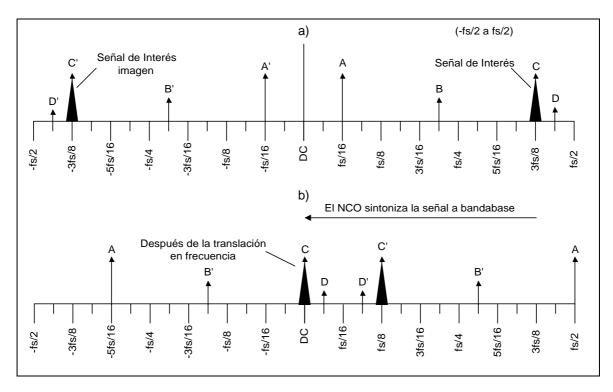

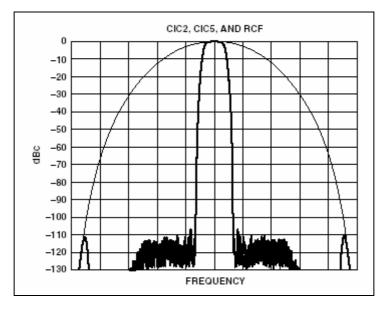

La primera consiste en emplear un sistema de evaluación, que usa un conversor A/D tipo *pipeline* de banda ancha y 14 bits (AD6644) y un receptor digital (AD6620), que tiene filtros FIR con tasas de decimación programables y cuenta con un oscilador numérico complejo, NCO, para trasladar a banda base y adquirir señales de alta frecuencia.

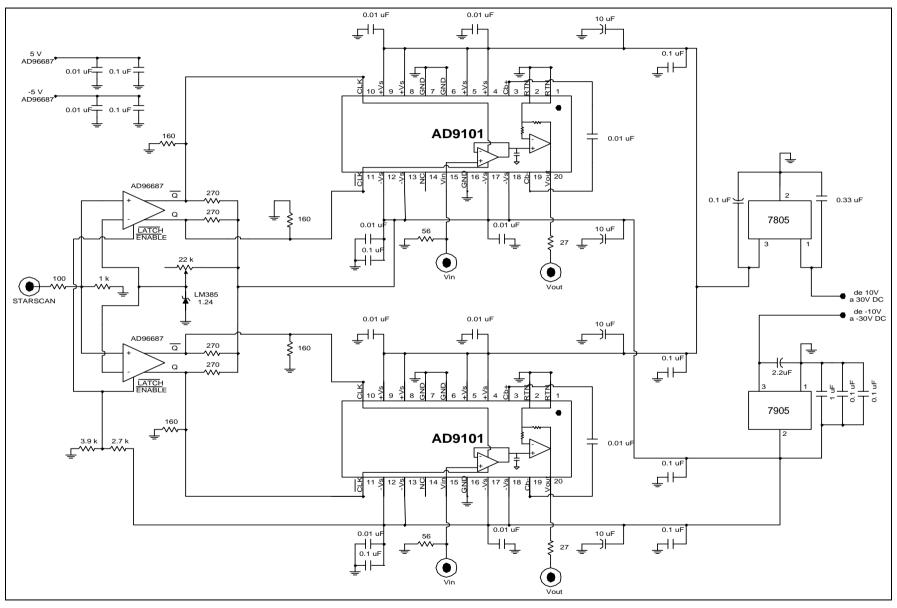

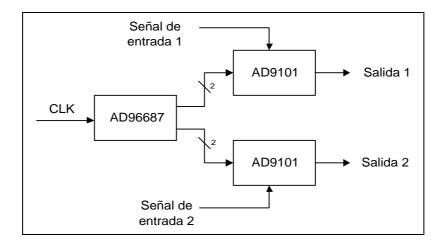

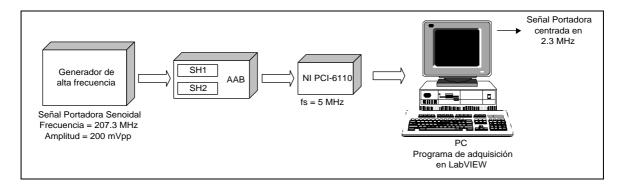

La segunda consiste en utilizar una tarjeta de adquisición comercial (NI PCI-6110), que cuenta con buena resolución para la obtención de datos, pero con el inconveniente de poseer un ancho de banda menor. Para resolver este problema, se decidió agregarle un circuito de muestreo y retención (*Sample and Hold*) a la entrada de la tarjeta.

La adición de este circuito (sincronizado y seleccionado adecuadamente) nos permitirá incrementar el ancho de banda de entrada del conversor A/D y en consecuencia, el del sistema de adquisición utilizado.

\_

<sup>&</sup>lt;sup>1</sup> Pipeline: Técnica de conversión A/D realizada en etapas multiples [3].

#### 1.2. Objetivos

A partir de las consideraciones anteriores se plantearon los siguientes objetivos.

a) Estudiar, analizar, comprobar y difundir el proceso de submuestreo.

Como se planteó, el proceso de submuestreo es una técnica alternativa para el procesamiento digital de señales pasobanda, que en la actualidad es poco estudiado en México y Latinoamérica. Por esta razón, la tesis pretende difundir de forma general y práctica sistemas de adquisición que se basen en este tipo de muestreo, para de esta forma facilitar su desarrollo, diseño e implementación en sistemas que permitan manipular sin tanta complejidad señales pasobanda de alta frecuencia, como las empleadas en sistemas de equipos Biomédicos y telefonía Celular Digital.

b) Evaluar dos sistemas de adquisición distintos basados en técnicas de submuestreo, con la finalidad de establecer la viabilidad de su aplicación en el procesamiento de señales de resonancia magnética nuclear o ultrasonido.

Basándonos en las tarjetas de adquisición de datos que actualmente se encuentran en el mercado, se busca desarrollar alternativas de procesamiento de señales pasobanda de alta frecuencia y con amplitudes pequeñas, empleando submuestreo, así como el desarrollo de un software propio de adquisición para evaluar estas alternativas.

Determinar las limitaciones y alcances de las dos alternativas de solución desarrolladas, con el propósito de establecer si pueden ser empleadas, en un futuro, como base del procesamiento de señales para sistemas biomédicos de gran utilidad como lo son la resonancia magnética nuclear o el ultrasonido.

#### c) Diseñar e implementar un circuito adaptador de ancho de banda (AAB)

Uno de los problemas principales en el manejo de señales pasobanda de alta frecuencia, mediante el uso de ciertas tarjetas comerciales, es el hecho de que algunas de éstas utilizan conversores A/D con anchos de banda de entrada estrechos. Esta limitante fue la causa por la que nos vimos en la necesidad de desarrollar un circuito que nos permitiera incrementar este ancho de banda en la tarjeta de adquisición NI PCI 6110 y poder así, manipular señales de alta frecuencia.

Dentro de este punto se incluye la evaluación de sus características y su desempeño dentro del sistema de adquisición.

#### 1.3. Estructura de la tesis

En este capitulo se ha buscado situar el presente trabajo dentro del contexto actual del manejo de señales, así como plantear las características generales del proceso de submuestreo, sus aplicaciones, y los requerimientos que su uso implica. Se plantean las alternativas de solución a ser evaluadas para la adquisición y el procesamiento de señales pasobanda, lo que nos permite determinar los objetivos generales de la tesis.

En el capitulo 2 se describen los fundamentos teóricos básicos empleados para el desarrollo y comprensión de la tesis. Se parte de los fundamentos generales del muestreo, pasando por el submuestreo, la modificación de la frecuencia de muestreo mediante la decimación, la cuantificación y su ruido asociado, además de una breve descripción de los diferentes tipos de conversores analógico – digital, en particular los conversores de alta velocidad, concluyendo con técnicas de procesamiento de señales, como la zFFT y la detección en cuadratura.

En el capítulo 3 se realiza la caracterización y calibración de los dos sistemas de adquisición empleados. Se describe la tarjeta de adquisición NI PCI-6110, explicando su funcionamiento y características, para después continuar con el circuito adaptador de ancho de banda implementado, indicando las diferentes pruebas realizadas para llegar a su diseño final. Después se describen y enumeran las características propias del sistema de adquisición AD6644 - AD6620 y las pruebas de calibración realizadas al mismo, para concluir con la presentación y explicación del software de adquisición empleado en cada uno de los métodos, así como el software desarrollado con el fin de obtener señales de RMN.

A continuación, en el capitulo 4, se presentan los resultados obtenidos durante el desarrollo de los experimentos propuestos, detallando las condiciones en las que fueron realizados y se hace una comparación entre las respuestas alcanzadas con cada uno de los sistemas.

Finalmente, en el capítulo 6, se dan las conclusiones obtenidas del trabajo desarrollado y las aportaciones encontradas, así como las posibilidades del empleo de esta técnica en futuros sistemas de adquisición.

#### 2. ASPECTOS TEÓRICOS

#### 2.1. Muestreo

El muestreo de una variable, es la operación de tomar muestras de la misma, es decir, es el proceso de discretizar una señal en tiempo. Esta idea general de muestreo, referida a sistemas de control mediante el uso de una computadora, se concreta en la toma de muestras de una señal continua en instantes periódicos de tiempo, a diferencia de otros procesos de muestreo donde el tiempo no es una variable a considerar, por ejemplo las muestras estadísticas para calcular la altura media de una población. El muestreo de señales que vamos a considerar consiste en la construcción de secuencias a partir de señales continuas, tomando como valores de las secuencias los correspondientes a la señal en instantes periódicos de tiempo.

La operación contraria es igualmente necesaria en sistemas de control con computadora. Tal operación consiste en construir, a partir de la secuencia generada en el muestreo, una señal continua con la que se logre "excitar" el sistema continuo. Este proceso inverso del muestreo se denomina reconstrucción de señales. Sin embrago, surge un nuevo problema, la pérdida de información de la señal original. Cabe pensar que si a partir de una señal continua únicamente tomamos valores en ciertos instantes, existe, en consecuencia, una pérdida de información, con lo que no se podrá reconstruir perfectamente la señal original a partir de la secuencia obtenida. Por lo que se toman varias medidas, fijadas en el teorema del muestreo, para reducir esta pérdida al mínimo como se verá más adelante.

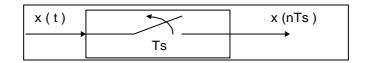

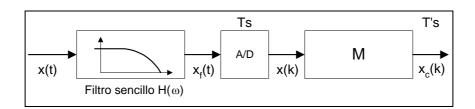

Entre los distintos tipos de muestreo, el que más destaca es el periódico, que se caracteriza porque los instantes de toma de muestras están regularmente espaciados. Este tipo de muestreo es el usado normalmente en el control de procesos por computadora. y está caracterizado por el intervalo de tiempo existente entre dos muestras sucesivas Ts, al que llamaremos *periodo de muestreo*, siendo su inverso, muestras por unidad de tiempo, la *frecuencia de muestreo*, fs. El elemento que realiza este proceso se denomina *muestreador* y se puede representar mediante el diagrama de bloques de la Figura 2.1.

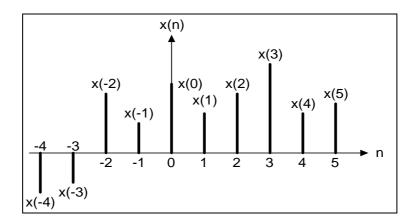

En este bloque la salida x(nTs), puede expresarse como:

$$x[n] = x(nTs)$$

...(Ec. 2.1)

donde: n = ..., -2, -1, 0, 1, 2, ..., e indica el n-ésimo término de la secuencia obtenida.

Figura: 2.1: Diagrama de bloques de un muestreador.

Se puede apreciar que el periodo de muestreo va a jugar un papel fundamental en este proceso, y de él dependerá en gran medida que se pierda información o no.

#### 2.1.1. Teorema del muestreo o Teorema de Nyquist

Al llevar acabo el proceso de digitalización de una señal analógica, se obtienen una serie de muestras tomadas a un ritmo determinado, de forma que estas puedan reemplazar a la señal analógica original (representación discreta de la señal) sin pérdida de información y puedan ser utilizadas para su reconstrucción.

El concepto de muestreo de una señal es la base para la representación discreta de una señal continua de banda limitada. Se fundamenta en el Teorema de Muestreo, desarrollado en 1928 por H. Nyquist y probado matemáticamente por Claude Shannon en 1949. La explicación de este teorema se reduce, como se verá a continuación, a su aplicación a señales limitadas en banda y considerando un muestreo uniforme, es decir, muestras espaciadas equidistantemente.

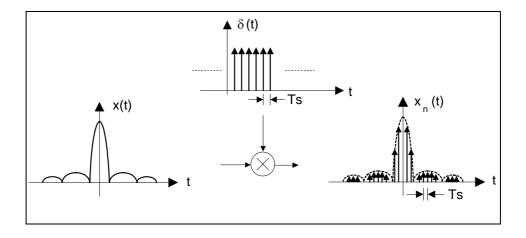

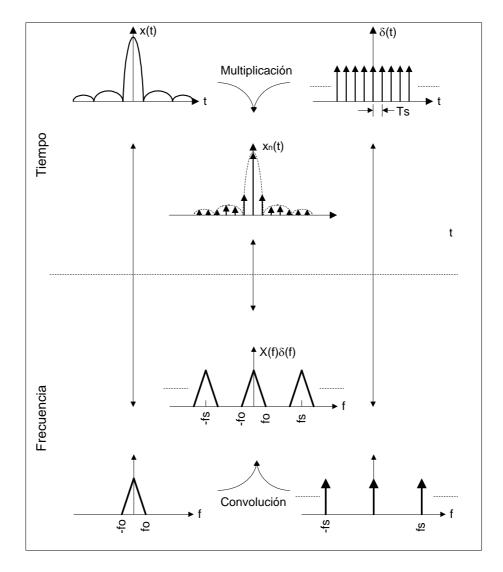

El teorema de muestreo se establece a partir del producto, en el dominio del tiempo, entre una señal limitada en banda x(t) y un tren de Deltas de Dirac  $\delta(t)$ , como se observa en la Figura 2.2, [5].

Figura 2.2: Teorema del muestreo o Teorema de Nyquist (muestreo ideal uniforme)

Para que este proceso de muestreo se lleve a cabo de una forma correcta, es necesario que la secuencia  $x_n(t)$ , obtenida como consecuencia del mismo (Figura 2.2), posea un número suficiente de muestras de tal forma que contenga toda la información relevante de la señal original.

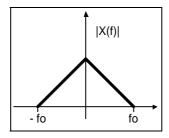

La señal continua x(t), posee un espectro en frecuencia X(f) que es nulo a partir de una determinada frecuencia fo, como el mostrado en la Figura 2.3. Las señales que cumplen esta condición se denominan "limitadas en banda".

Figura 2.3: Espectro de la señal limitada en banda x(t).

Si a x(t) se le toman muestras a un mismo intervalo de tiempo, denominado como Ts y definido por:

$$Ts > \frac{1}{2f_0}$$

...(Ec. 2.2)

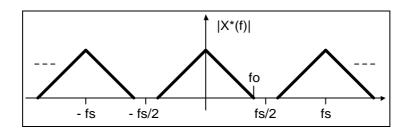

el espectro en frecuencia de la secuencia debida al proceso de muestreo será de la forma indicada en la Figura 2.4

Figura 2.4: Espectro muestreado de la señal limitada en banda x(t). (Ts > 1/2fo)

La función periódica  $X^*(f)$  tendrá como función básica X(f), con lo cual a partir de  $X^*(f)$  es inmediato conocer X(f) y por tanto su representación en el tiempo x(t).

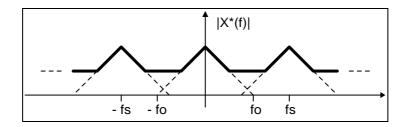

Si por el contrario, el periodo de muestreo es Ts < 1/2 fo, el espectro de la secuencia será de la forma indicada en la Figura 2.5, donde se aprecia que el periodo

básico de la función  $X^*(f)$  no coincide con X(f), y por tanto no es posible reconstruir la señal continua a partir de esta secuencia.

Figura 2.5: Espectro muestreado de la señal limitada en banda. (Ts < 1/2fo)

Con base en el proceso descrito anteriormente, el teorema fundamental del muestreo se puede concretar de una manera formal en el siguiente enunciado:

"Si una señal continua x(t) tiene una banda de frecuencia tal que fo sea la mayor frecuencia contenida dentro de dicha banda, dicha señal podrá reconstruirse sin distorsión a partir de muestras de la señal tomadas a una frecuencia fs siendo fs > 2fo", [8]. En otras palabras, una señal analógica puede ser reconstruida, sin error, a partir de muestras tomadas en intervalos iguales de tiempo. La razón de muestreo debe ser igual o mayor al doble del ancho de banda de la señal analógica, en banda base.

A la frecuencia fs = 2fo se le denomina frecuencia de Nyquist, al periodo de muestreo Ts, periodo de Nyquist; y a este tipo de muestreo se le conoce como muestreo ideal uniforme; (para más detalles ver Anexo 1)

Como corolario del teorema puede afirmarse que dada una colección discreta de valores x(n/2fo) existe una función x(t) y solo una de banda limitada a fo que pasa por todos los puntos dados y que se construye mediante la fórmula de interpolación. Existen infinitas funciones que pasan por esos puntos y son de anchura diferente de fo. Por lo tanto, para la reconstrucción de la señal a partir de sus muestras, es necesario que la frecuencia de muestreo sea superior al doble de la frecuencia máxima que se desea obtener.

Es conveniente aclarar que el muestreo ideal, como su nombre lo indica, es un tipo de muestreo no realizable de manera física ya que es imposible "fabricar" un tren de impulsos periódicos. Por esta razón este tipo de muestreo se presenta únicamente de manera ilustrativa para dar a entender el proceso de conversión analógica - digital.

Resumiendo de forma esquemática y general, el muestreo ideal uniforme puede ser representado tanto en el dominio del tiempo como en el dominio de la frecuencia, por medio de la Figura 2.6.

Figura 2.6: Muestreo ideal uniforme.

#### 2.1.2. Aliasing o solapamiento espectral.

Una vez planteado el teorema, se pueden hacer dos observaciones:

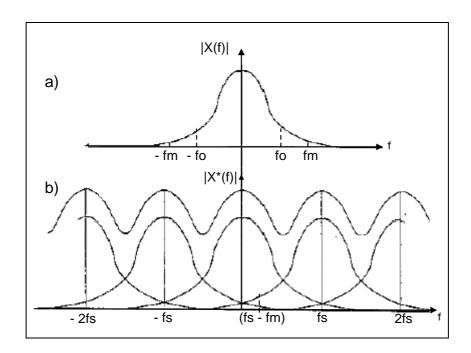

1. La mayoría de las señales no están estrictamente limitadas en banda (esto es cuando la transformada X(f) de una señal continua, no se anula a partir de un cierto valor en frecuencia), aunque la amplitud de su espectro decae para frecuencias elevadas

- (Figura 2.7a). En el análisis de señales no existe una limitación estricta en banda debido a que gran parte de las señales reales son de duración finita en tiempo.

- 2. Si se considerará el caso de tener Ts < 1/(2fo) sería necesario emplear un filtro pasobajas ideal para reconstruir aunque sea la parte menos encimada del espectro de la señal analógica (Figura 2.7b), y este filtro no es realizable.

Por estos motivos el proceso de muestreo introduce una distorsión irreversible, que impide recuperar la señal original en forma exacta.

Figura 2.7: Espectro muestreado de la señal no limitada en banda.

Sin embargo y a pesar de estas consideraciones, las señales que no se encuentran estrictamente limitadas en frecuencia pueden ser tratadas como limitadas en banda si el contenido espectral que excede el intervalo (-fo, fo) es pequeño o escasamente significativo (Figura 2.7a).

Ahora bien, al muestrear esta señal (Figura 2.7b) la distorsión se hace presente. En el proceso de reconstrucción de la señal, las frecuencias inferiores a fs – fo del espectro centrado en fs, que originalmente estaban fuera de la banda de interés BW = (0, fo), aparecen ahora de la forma (fs – fm) < BW. Este fenómeno ocurre con cualquier frecuencia submuestreada, es decir, cualquier fm que cumpla con la condición: fs < 2fm. Cuando se cumple dicha condición, se genera el efecto de procesamiento denominado solapamiento o "aliasing".

La única forma de combatir este efecto es aumentar convenientemente la frecuencia de muestreo de acuerdo con el teorema de Nyquist, de forma que los componentes fuera de la banda de interés se presenten muy atenuados y su influencia sea apenas perceptible.

#### 2.1.3. Muestreo con pulsos de duración finita

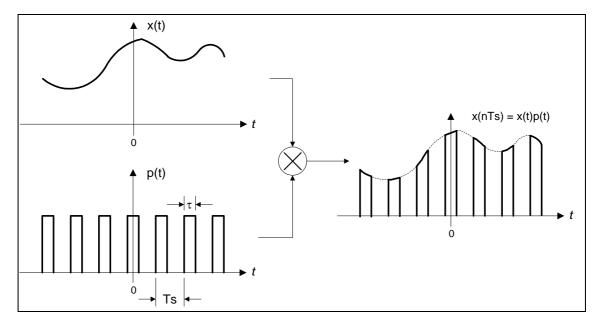

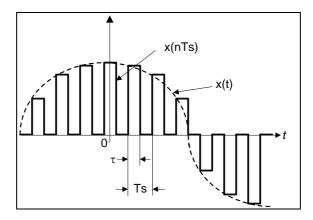

El muestreo ideal, como se mencionó anteriormente, es un tipo de muestreo que solo puede llevarse a cabo de forma teórica, pues en él las muestras se adquieren empleando un tren de impulsos que es imposible realizar físicamente. Por esta razón es necesario llevar a cabo una adecuación práctica de este tipo de muestreo considerando que la función muestreadora sea un tren de pulsos (y no funciones impulso o Delta de Dirac) de duración fínita. A este tipo de muestreo se le conoce como muestreo natural y su esquema funcional se muestra en la Figura 2.8

En el muestreo natural se multiplica una señal analógica x(t), por un tren periódico de pulsos rectangulares p(t). La salida x(k), puede ser interpretada como una serie de pequeñas ventanas en el tiempo con duración  $\tau$ , durante las cuales la señal a muestrear atraviesa un muestreador.

Figura 2.8 Muestreo con pulsos de duración finita o muestreo natural.

Entonces, sabiendo que la señal muestreadora es una señal periódica que se puede representar mediante una serie de Fourier [8], la señal resultante del muestreo será:

$$x(nTs) = x(t)p(t) = C_0x(t) + \sum_{n=1}^{\infty} C_nx(t)Cos(2\pi nFst)$$

...(Ec. 2.3)

La relación entre X(f) y  $X_s(f)$ , transformadas de x(t) y x(nTs), respectivamente vendrá dada por:

$$F(x(nTs)) = X_s(f) = C_0 X(f) + \sum_{n=1}^{\infty} C_n F(x(t)Cos(2\pi nFst))$$

...(Ec. 2.4)

El término  $F[x(t)Cos(2\pi nFs\ t)]$  corresponde a una modulación en AM de la señal x(t), por lo que aplicando la transformada de una multiplicación de señales obtenemos [8]:

$$F[x(t)Cos(2\pi nFst)] = \frac{1}{2}[X(f - nFs) + X(f + nFs)] ...(Ec. 2.5)$$

Por lo que la trasformada total sería:

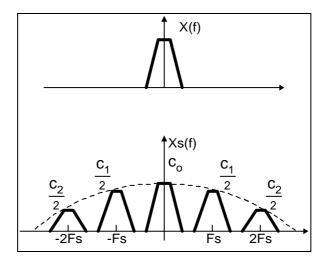

$$X_s(f) = C_0 X(f) + \sum_{\substack{n=-\infty\\n\neq 0}}^{\infty} \frac{1}{2} C_n X(f - nFs)$$

...(Ec. 2.6)

A diferencia del muestreo ideal, los componentes espectrales repetidos en los armónicos de fs quedan afectados en amplitud (distorsión de amplitud) por el valor de los coeficientes  $C_n$ , que tienden a ir disminuyendo a medida que aumenta la frecuencia. Nótese que si  $\tau$  tiende a cero, es decir, la duración de los pulsos mostrados en la Figura 2.8 el muestreo natural tiende a ser el ideal, pues los pulsos dejarían de serlo, para convertirse en impulsos.

Con ello, el espectro en frecuencia de la señal muestreada corresponderá con el mostrado en la Figura 2.9

Figura 2.9 Espectro de una señal muestreada con pulsos de duración finita

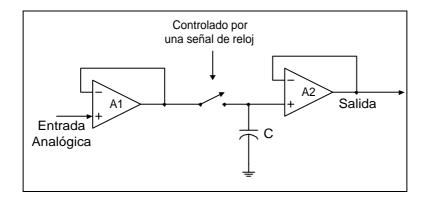

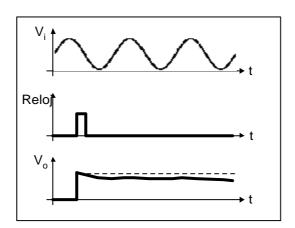

Como se demostró, el muestreo con pulsos de duración finita corresponde a una modulación en amplitud, la cual, es similar a la llamada modulación por amplitud de pulsos (PAM, *Pulse Amplitude Modulation*), sin embargo, en el muestreo natural la parte superior de cada pulso rectangular modulado varía con la señal x(t), en tanto que en las señales PAM esa parte se mantiene plana [9]. En realidad, la PAM es un caso especial del muestreo natural conocido también como muestreo de tope plano.

Para llevar a cabo la generación de una señal PAM se tienen que seguir dos operaciones:

- 1. Muestreo instantáneo de la señal analógica de entrada x(t).

- 2. Alargamiento de la duración de cada muestra hasta cierto valor constante  $\tau$ , como se ilustra en la Figura 2.10

En la tecnología de circuitos digitales se hace referencia en forma conjunta a estas dos operaciones como "muestreo y retención" (*sample and hold*).

Figura 2.10 Muestreas de tope plano (PAM), representando una señal analógica

Una razón importante del alargamiento intencional de la duración de cada muestra es evitar el uso de un ancho de banda de canal excesivo, ya que el ancho de banda es inversamente proporcional a la duración del pulso, [9].

Este tipo de muestreo presenta la ventaja de ser más inmune al ruido que el muestreo natural, sin embargo, al igual que en este, se introduce distorsión de amplitud. Para disminuirla se debería disminuir el valor de  $\tau$ , pero eso también disminuye la amplitud de la señal. Lo que se estila es usar un  $\tau$  intermedio de acuerdo a las necesidades del sistema empleado. [7]

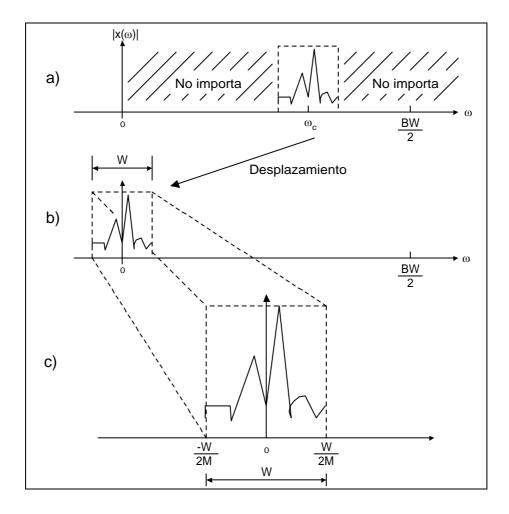

#### 2.1.4. Muestreo pasobanda<sup>2</sup>

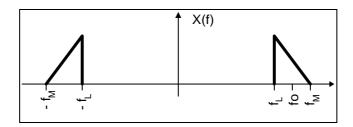

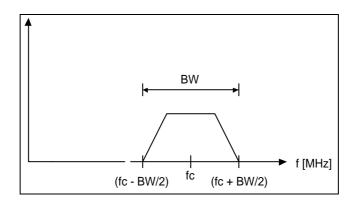

Si se supone una señal limitada en bada x(t) tal que su espectro X(f) sea como el mostrado en la Figura 2.11:

Figura 2.11: Espectro de una señal pasobanda.

en donde:  $f_M$  es el máximo componente frecuencial contenido en el espectro X(f) y  $f_L$  es el mínimo componente frecuencial contenido en el espectro X(f).

Y si además se definen las siguientes ecuaciones:

$$BW = f_M - f_L$$

...(Ec. 2.7)

$k = \frac{f_M}{BW}$  ...(Ec. 2.8)

$k - 1 = \frac{f_L}{BW}$  ...(Ec. 2.9)

en donde: BW corresponde al ancho de banda de la señal y k es la posición de la banda en el espectro

Entonces, de acuerdo con las consideraciones antes descritas, es posible afirmar que: siempre que el ancho de banda de la señal sea menor que  $f_L$ , es posible muestrear a una frecuencia menor que la que impondría Nyquist, siempre y cuando se garantice que las repeticiones espectrales no se superponen con el espectro X(f) en aquellas regiones espectrales donde se encuentra información de interés.

Por lo tanto, para que no exista solapamiento, de forma que x(t) pueda ser rescatado con un filtro pasobanda, se debe cumplir que:

$$-f_L + (N-1)Fs \le f_L$$

...(Ec. 2.10)

$-f_M + NFs \ge f_M$  ...(Ec. 2.11)

-

<sup>&</sup>lt;sup>2</sup> Referencia bibliográfica: [7]

$$\frac{2f_M}{N} \ge Fs \le \frac{2f_L}{N-1} \dots (\text{Ec. 2.12})$$

$$\frac{2kBW}{N} \le Fs \le \frac{2(k-1)BW}{N-1} \dots (\text{Ec. 2.13})$$

$$k \ge N$$

donde N = 1, 2, 3 ..., k, y determina la cantidad de veces que puede repetirse el espectro sin superponerse. Con base en estas ecuaciones puede concluirse que:

Dado el espectro X(f), se obtiene  $f_L$  y  $f_M$ , y por ende BW y k. Con esto se definen los posibles valores de N y finalmente es posible determinar la frecuencia de muestreo. Este proceso puede ser ilustrado esquemáticamente mediante la Figura 2.12:

Figura 2.12: Submuestreo de una señal pasobanda.

Para ejemplificar de forma práctica las ecuaciones obtenidas en la deducción anterior, considérese el siguiente ejemplo: Si se supone que X(f) tiene la forma de una señal pasobanda como la ilustrada en la Figura 2.12, con  $f_L$ = 3,000 Hz;  $f_M$  = 4,000 Hz. Por lo tanto BW =1,000 Hz. De esta forma k = 4 y N puede tomar los siguientes valores 1, 2, 3 y 4. Al aplicar la ecuación 2.13 que define el rango de valores de fs, se tiene:

$$\frac{2(4)BW}{N} \le Fs \le \frac{2(3)BW}{N-1}$$

...(Ec. 2.14)

$$\frac{8BW}{N} \le Fs \le \frac{6BW}{N-1}$$

...(Ec. 2.15)

Ahora, con:

$$N = 1$$

$8BW \le Fs \le \infty$  ...(Ec. 2.16)

$N = 2$

$4BW \le Fs \le 6BW$  ...(Ec. 2.17)

$N = 3$

$\frac{8BW}{3} \le Fs \le 3BW$  ...(Ec. 2.18)

$N = 4$

$2BW \le Fs \le 2BW$  ...(Ec. 2.19)

Por lo tanto en este caso se puede muestrear a 2 kHz (caso con N=4, Ec. 2.19), valor menor que el establecido por el teorema de Nyquist (el cual correspondería a 8 kHz, caso con N=1, Ec. 2.16) y recuperar la señal con un filtro pasobanda. En este sentido, puede observarse que mientras quepan más repeticiones entre 0 y  $f_L$  es posible bajar cada vez más la frecuencia de muestreo.

Muchas de las señales con interés práctico suelen ser señales pasobanda, por lo que el construir un sistema de procesamiento que utilice el muestreo pasobanda de tal forma que no se pierda información relevante, es una solución óptima dentro de diversos campos del procesamiento de señales.

# 2.2. Modificación de la frecuencia de muestreo<sup>3</sup>

Al adquirir, mediante un conversor A/D, una señal x[n] = x(nTs), no siempre se desea tener las muestras en todos los instantes de tiempo que son múltiplos del periodo de muestreo Ts, sino que algunas veces, solo se necesita tener x[n] = x(nT') siendo T' = kTs. Dependiendo de si el valor de k es mayor o menor que la unidad, se afronta un problema de decimación o de interpolación de la señal muestreada. La decimación, conocida también como diezmado, consiste en la obtención de una nueva secuencia de muestras con una velocidad de muestreo entre ellas, inferior a la que se ha utilizado en su adquisición. Esta operación podría parecer absurda a primera vista: ¿Para qué despreciar muestras ya adquiridas, con un conversor A/D de una cierta velocidad, si después se ignoran muestras emulando a un sistema de menor velocidad de adquisición? En realidad parece bastante extraño que, una vez adquirido un conversor, se decida "desperdiciarlo" no considerando todas las muestras. Si el

<sup>&</sup>lt;sup>3</sup> Referencia bibliográfica:[8]

motivo de no considerar todas las muestras es que las operaciones que tiene que ejecutar la microcomputadora son complejas y, consecuentemente, lentas, no hacia falta seleccionar un conversor con tanta velocidad de muestreo.

En ocasiones es preferible adquirir muestras a una velocidad superior a la estrictamente necesaria según la condición de Nyquist, dándose la paradoja de que de esta forma puede abaratarse el diseño de los conversores A/D o el de algún otro subsistema. Tal es el caso de los filtros antitraslape (antialiasing), que introducen menos distorsiones de cruce y de solapamiento si se aumenta la velocidad de muestreo, aunque después se haga una decimación de las muestras para disminuir la velocidad de su posterior procesamiento. O bien puede pensarse en los conversores A/D de 1 bit: si al mismo tiempo que se reduce el número de bits del conversor (lo cual lo abarata) se aumenta la velocidad de muestreo, la relación señal a ruido de cuantificación del conversor se puede mantener constante [8]. La adquisición de muestras a una velocidad superior a la teórica (proceso de sobremuestreo o de oversampling) puede presentar ventajas en el diseño electrónico en algunos tipos de conversores. El precio es que, una vez adquiridas las muestras, la velocidad de procesado debe ser alta también; con lo que las ventajas que se tuvieron en el diseño de los subsistemas de adquisición se pagan en el costo de los microprocesadores, que deben ser veloces, y de las memorias, cuyo tiempo de acceso debe ser muy rápido. En casos como este, es cuando aparece la decimación: eliminando muestras después de la adquisición se evita el problema de velocidad en el procesado.

Existen otras líneas de aplicaciones de la decimación en las que ésta aparece de forma natural, sin que sea para compensar un sobremuestreo previo, por ejemplo, la codificación en sub bandas utilizada en equipos de audio digital.

La interpolación es el caso contrario a la decimación, en la cual se efectúan los procesos de intercalar muestras entre cada par de muestras de la secuencia original y de aplicar un filtro interpolador a la secuencia así obtenida. Con ello se obtiene una secuencia con muestras intercaladas cuya velocidad de muestreo aparentemente es mayor que la real; en los puntos donde no se ha efectuado un muestreo físico se interpreta que el valor de las muestras es el calculado (o fijado a cero, según los casos). Filtrando adecuadamente la secuencia intercalada se consigue una mejor reconstrucción de la señal, siendo esto de gran utilidad para simplificar el diseño de los filtros reconstructores que siguen al conversor D/A en la etapa de salida analógica. Ambos procesos, el de decimación y el de interpolación, modifican la velocidad de muestreo de las señales originales. Por ello se les denomina como procesado multi-tasa (*multirate*).

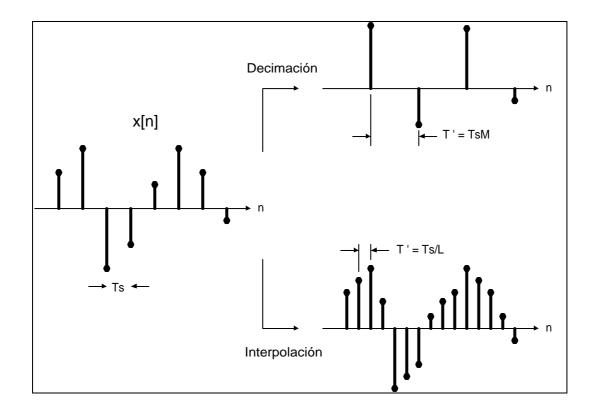

Como se mencionó al comienzo de este apartado, si el valor que toma k es mayor o menor que la unidad se enfrentan dos situaciones diferentes:

a) Interpolación: k = 1/L < 1 (upsampling).

Donde L es el factor de disminución del periodo de muestreo Ts, como lo muestra la Figura 2.13

b) Decimación: k = M > 1 (downsampling).

Donde M es el factor de incremento del periodo de muestreo Ts, como lo muestra la Figura 2.13

Figura 2.13: Decimación e Interpolación

Debido a los alcances que la presente tesis persigue, la atención se centrará en la decimación. La interpolación solo se mencionará cuando sea necesario, dejando al lector la consulta particular de este tema con la ayuda de la bibliografía presentada, [8].

#### 2.2.1. Decimación

Si de cada M muestras tan solo se toma una, es como si se pasara de un periodo de muestreo Ts a uno M veces mayor, lo que equivale a una disminución de la frecuencia de muestreo. Como el efecto es una compresión de la velocidad de muestreo, a la constante k se le denomina factor compresor.

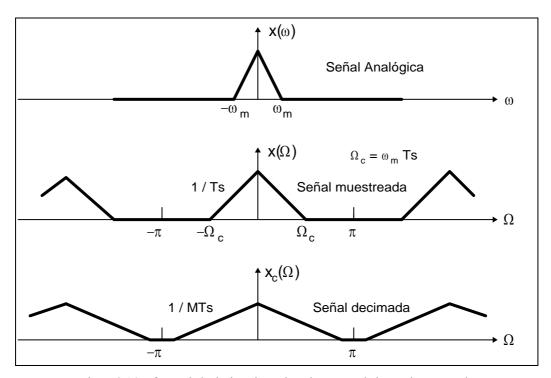

El efecto producido, en el dominio de la frecuencia, es una expansión de las imágenes repetidas de la señal muestreada. Si se ha muestreado una señal analógica cuya frecuencia máxima es  $\omega_m$  con un periodo de muestreo Ts, el espectro en banda base de la señal muestreada ocupará hasta una frecuencia  $\Omega_c = \omega_m Ts$ . Si se cambia esta Ts por una mayor, T' = MTs, el espectro ocupará hasta otra frecuiencia  $\Omega = \omega_m T'$ , es decir, M veces mayor que la  $\Omega$  anterior. Este efecto se muestra en la Figura 2.14.

Figura 2.14: Efectos de la decimación sobre el espectro de la señal muestreada

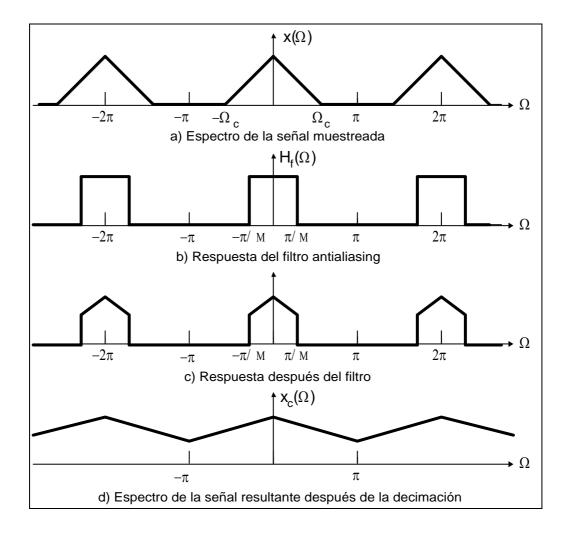

Pero a partir de ciertos valores de M se producirá traslape, ya que si se eliminan demasiadas muestras es como si no se hubiera respetado la condición de Nyquist en su adquisición. El caso límite para no tener traslape es cuando  $\Omega = \omega_m T' = \omega_m MTs = \pi$

Si es necesario utilizar un valor de M elevado, puede reducirse este problema mediante filtros *antialiasing* tal como se muestra en la Figura 2.15, donde  $H_f(\Omega)$  representa la respuesta del filtro *antialiasing* (Figura 2.15b). La respuesta obtenida después del filtrado de la señal muestreada  $x(\Omega)$ , se observa en la Figura 2.15c. Una vez hecho esto se realiza un proceso de decimación resultando en la señal  $x_C(\Omega)$  (Figura 2.15d).

Figura 2.15: Filtrado antialiasing o antitraslape

En general, se necesitaran filtros *antialiasing* para la decimación si:

$$M > (\pi / \Omega_c)$$

...(Ec. 2.20)

En el caso de que k sea un número no entero, el primer paso es representarlo como el cociente de dos número enteros M y L, de la forma k = M / L. Por lo anteriormente visto, esto puede interpretarse como un sistema de interpolación (que dará el factor 1/L) en cascada con un sistema de decimación (que dará el factor M).

#### 2.2.2. Decimación aplicada a la conversión A/D: Simplificación de los filtros antialiasing.

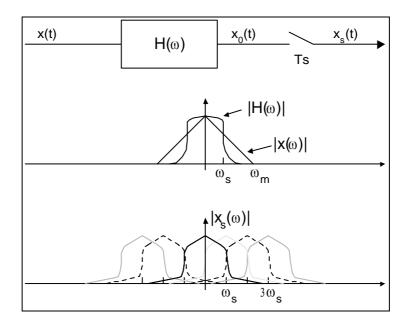

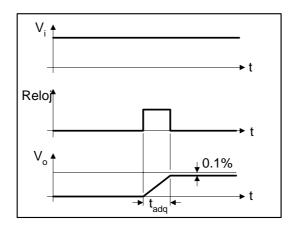

Supongamos un filtro *antialiasing* no ideal  $H(\omega)$ , con una cierta pendiente de caída, utilizado para limitar en banda a una señal x(t) cuya frecuencia máxima es  $\omega_m$ . El motivo del filtrado es que la máxima frecuencia muestreable con el conversor es de  $\omega_s$  rad/s.

Figura 2.16: Efectos de un filtro antialiasing real (analógico)

Como se puede apreciar en la Figura 2.16, el filtro produce una deformación de las amplitudes del espectro de la señal (por no ser un filtro ideal), además de distorsiones de solapamiento y de cruce (por tener una banda de transición con poca pendiente). Para evitar estas distorsiones del filtro, se pueden usar filtros analógicos de orden elevado, lo que conlleva un costo elevado. Una solución alternativa es sobremuestrear la señal x(t), de tal forma que las repeticiones armónicas en frecuencia queden más separadas entre sí. De este modo, al haber menos probabilidad de traslape, los filtros son más sencillos, o incluso, pueden llegar a ser innecesarios. A continuación de la etapa de muestreo se situará un sistema de decimación, para así obtener las muestras que realmente necesitamos para el posterior procesado de la señal, como lo muestra la Figura 2.17.

Figura 2.17: Diagrama de bloques de un proceso de sobremuestreo y posterior decimación para la simplificación de un filtro antitraslape.

#### 2.3. Cuantificación

#### 2.3.1. Aproximación a la teoría de la cuantificación

La cuantización o cuantificación de una señal muestreada x(nTs) es un fenómeno derivado de la aritmética finita de las computadoras (número de bits), que impide que estas puedan trabajar con una resolución infinitesimal.

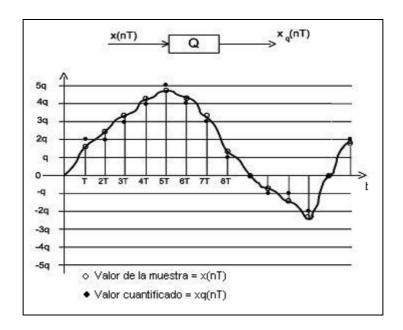

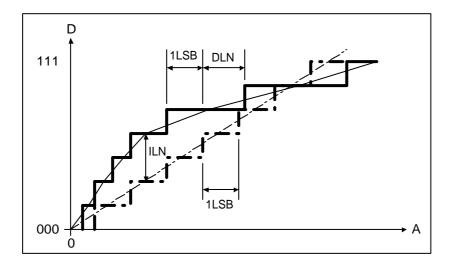

Consiste en representar la señal muestreada x(k) mediante una serie finita de niveles de amplitud, asignándose a cada muestra el valor más próximo a ella, dentro de una escala de valores fijos y conocidos. Denominando x(nTs) al valor de una muestra, y a  $x_q(nTs)$  al valor cuantificado de ésta, el resultado de la cuantificación de una señal sería el que se muestra en la Figura 2.18. [8]

Figura 2.18: Diagrama de bloques y representación gráfica de la cuantificación de una señal, en donde q = nivel cuántico ó intervalo de cuantificación.

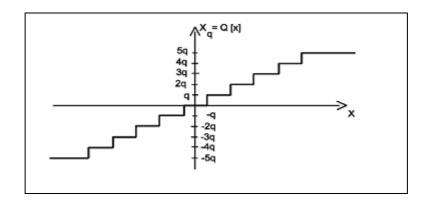

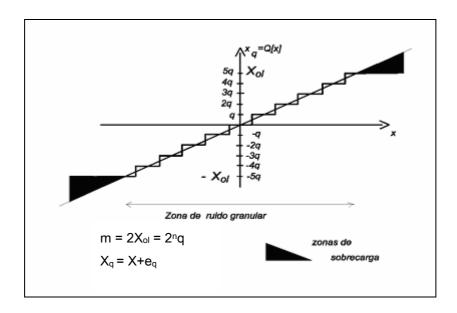

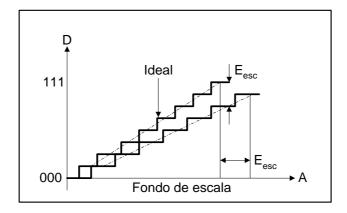

La característica entrada-salida del cuantificador Q anterior, donde se ha supuesto uniforme la distribución de los niveles cuánticos, es la que se muestra en la Figura 2.19.

El valor de q se denomina intervalo de cuantificación y coincide con la diferencia entre el mayor y menor valor de la entrada a los que se les asigna el mismo estado de salida.

Este caso corresponde a la característica de un cuantificador uniforme, ya que los niveles q aparecen equiespaciados.

Figura 2.19: Característica entrada-salida de un cuantificador

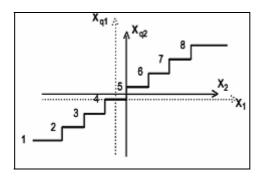

El número de estados de salida expresados en número de bits (n), determina la resolución del cuantificador. Debido a que los circuitos lógicos solamente poseen dos estados (cero y uno), el número de niveles cuánticos es un número par, dado por 2<sup>n</sup>. Así con 3 bits podremos cuantificar 8 niveles (Figura 2.20).

Figura 2.20: Cuantificador de 3 bits

En la figura anterior pueden apreciarse dos opciones al cuantificar, dependiendo del eje qué se escoja  $(X_1 \circ X_2)$ :

- El eje X<sub>1</sub> corresponde a un cuantificador uniforme no simétrico, ya que para X<sub>1</sub>>0 hay más niveles que para X<sub>1</sub><0. También es conocido como cuantificador *midtread*.

- El eje X<sub>2</sub> es un cuantificador uniforme simétrico. Este es el más usual [8] aunque tiene el inconveniente de no tener un nivel específico para el valor cero, que puede fluctuar entre dos niveles cuánticos. También se le conoce como *midrise*.

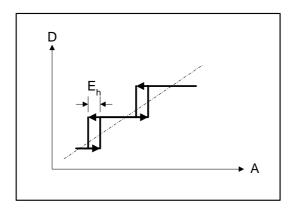

#### 2.3.2. Ruido de cuantificación

La cuantificación introduce inevitablemente un error, ya que si se intenta reconstruir la entrada a partir de la salida del cuantificador, no se obtiene el continuo de valores dentro del margen de entrada "m" (diferencia entre el mayor y menor valor de la entrada x(nTs)). Es decir, la salida del cuantificador  $x_q(nTs)$  no permite reconstruir exactamente a la entrada x(nTs). Por tanto se puede considerar que la salida del cuantificador será igual al valor de la entrada, más un termino de error, conocido como error de cuantificación. En este, se pueden diferenciar dos aspectos (Figura 2.21) [8]:

Figura 2.21: Errores de cuantificación, donde n = número de bits.

- Distorsión de sobrecarga (*overload*): es el error que se comete para valores de entrada fuera del margen m. El efecto es similar al que ocurre con dispositivos electrónicos saturados.

- Ruido de cuantificación (granular): corresponde al error cometido dentro del margen de valores de entrada permitido m. El máximo error que se pueda tener será ±q/2

Para señales aleatorias, es decir, que no pueden expresarse mediante procedimientos determinísticos y que solo son caracterizadas por medio de sus propiedades estadísticas o espectrales, las características que presenta el ruido de cuantización son [10]:

1. El ruido de cuantificación es blanco. Es decir, el error cometido en una muestra es estadísticamente independiente del error cometido en otra muestra.

- 2. El ruido de cuantificación no está correlacionado con la señal de entrada.

- 3. La distribución de los errores de cuantificación es uniforme sobre cada intervalo de cuantificación.

Para las señales periódicas, en cambio, la señal de error también es periódica. Esta señal de error incluye armónicos de la señal de entrada analógica dando como resultado distorsión armónica. Además, los armónicos que caen por arriba de la frecuencia de Nyquist aparecen en la banda de Nyquist en forma de traslape. La técnica comúnmente usada para reducir esta distorsión armónica es conocida como *Dithering*, la cual consiste en introducir una pequeña cantidad de ruido aleatorio a la señal analógica, provocando la distribución normal del ruido [11]. En una de las implementaciones que tiene esta técnica, el ruido térmico es sumado a la entrada del ADC para producir una potencia de ruido relativamente plana en el espectro por arriba del ancho de banda de Nyquist; así, el ruido térmico y el de cuantificación sumados provocan que el error de cuantificación sea uniforme, [12].

En los convertidores analógicos-digitales (ADC) más usados para procesamiento de señales de radiofrecuencia o de frecuencia intermedia, se emplea cuantificación uniforme, pues en ella existe la misma diferencia de voltaje entre cada nivel de cuantificación y la distribución del error de cuantificación es uniforme sobre cada intervalo de cuantificación. Tomando esto como base, se puede decir que la potencia rms del ruido de cuantificación  $P_{qn}$  es:  $P_{qn} = q^2/(12R)$ , donde R es la resistencia de entrada del convertidor analógico-digital. En un ADC ideal, esta representación de la potencia del ruido de cuantificación es adecuada para señales de entrada en dB que no se encuentran relacionadas con el reloj de muestreo.

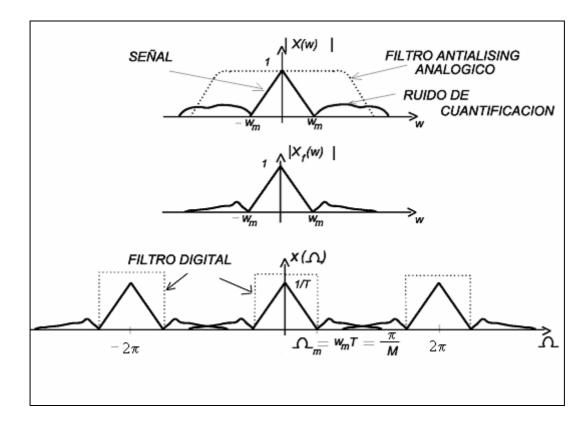

#### 2.3.3. Efectos de la decimación sobre el ruido de cuantificación

Cuando alrededor del espectro de una señal aparece ruido de alta frecuencia, como es el caso de algunos conversores sigma-delta donde aparece ruido de cuantificación importante, se efectúa un proceso de filtrado digital seguido de uno de decimación de la señal de salida del filtro, que permite márgenes dinámicos superiores a los 80 dB. La gráfica de un conversor A/D basado en modulación sigma-delta, con filtrado digital de la salida del modulador, se muestra en la Figura 2.22.

Figura 2.22: Espectro de las señales de un conversor A/D "de 1 bit" que consta de las siguientes etapas: Filtro antialiasing, modulador sigma-delta, filtro pasobajas digital y decimador.

Gracias a la acción del filtro antialiasing, el ruido de señal a altas frecuencias es disminuido, por lo que aplicando un filtro digital seleccionado en la frecuencia correspondiente al ancho de banda de interés y realizando un proceso de decimiación posterior, la señal final obtenida estará prácticamente limpia de ruido de cuantificación.

#### 2.4. Conversores A/D

Muchas variables físicas, como las eléctricas, son de naturaleza analógica y pueden tomar cualquier valor dentro de un rango continuo de valores. Esto implica que una señal analógica posee un número infinito de valores dentro de un intervalo de tiempo determinado, lo que la vuelve difícil de manejar.

En cambio, las señales digitales tienen un valor que se especifica por una de varias posibilidades previamente definidas, por ejemplo, para una señal digital binaria, su valor se determinará únicamente, con dos posibles estados: ALTO o BAJO. En la práctica, un valor digital representa a todo un rango específico de valores analógicos. Además, las señales digitales presentan tres ventajas principales respecto a las analógicas: son fáciles de procesar y se adaptan, de igual manera, a diferentes interfaces,

presentan gran inmunidad al ruido y es mucho más sencilla la determinación del valor de la señal contra un nivel de referencia, por lo que son fáciles de medir y valuar.

Cualquier información que tenga que introducirse en un sistema digital, primero debe de ponerse en forma digital para poder procesarla. Debido a que muchas de las señales que se necesitan introducir a sistemas digitales (como la computadora), son de carácter analógico, el empleo de un dispositivo que permita realizar la conversión entre un tipo de señales y otro, es indispensable. Este dispositivo es el conversor, que puede ser analógico – digital (A/D), si se necesita introducir una señal analógica a un sistema digital, o digital – analógico (D/A), si las necesidades caen en el caso contrario. [13]

En el caso de esta tesis, nos enfocaremos nuestro estudio en el conversor A/D debido a las características que posee dentro de los sistemas que se describirán en el capítulo siguiente.

En la actualidad se encuentran fácilmente en el mercado distintos tipos de conversores A/D. Todos ellos realizan la misma función (convertir una señal analógica en una digital), pero mediante procesos diversos, por lo que poseen características diferentes. Los más comunes son:

- Conversor A/D por contadores.

- Conversor A/D de cuenta continua.

- Conversor A/D con integrador.

- Conversor A/D de rampa discreta.

- Conversor A/D de balance continuo.

- Conversor A/D de aproximaciones sucesivas.

- Conversores A/D de alta velocidad

Para consultar las características generales de los conversores A/D, se incluye el anexo 2.

Debido a los alcances y objetivos que la presente tesis persigue, los únicos conversores que se describirán a continuación son los conversores A/D de alta velocidad, recomendando al lector la bibliografía marcada con el número [13], en el caso de interesarse por algún otro tipo de conversor.

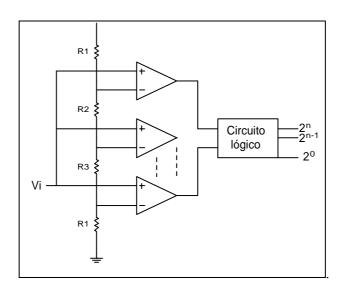

# 2.4.1. Conversores A/D de alta velocidad<sup>4</sup>

En esta sección se detallan los conversores A/D que se emplean en procesamiento de alta velocidad, lo que les permite utilizar tasas de muestreo elevadas.

Los conversores A/D de alta velocidad, son utilizados en una gran cantidad de aplicaciones de Procesamiento Digital de Señales. Las razones principales del uso de estos dispositivos es su alta velocidad de procesamiento y la disminución paulatina de su costo.

Este tipo de conversores fueron utilizados inicialmente en sistemas de instrumentación, así como en aplicaciones de procesamiento en las que la respuesta del sistema en el dominio del tiempo era de gran importancia. Actualmente, su aplicación se ha extendido hasta los sistemas de comunicaciones, en los que la respuesta en el dominio de la frecuencia también es importante.

Algunas de las características principales de este tipo de conversores, se enlistan a continuación.

- Alta velocidad de procesamiento y costo reducido

- Poco consumo de alimentación y potencia.

- Gran funcionalidad con otros dispositivos: *sample and hold*, compuertas programables, Filtros Digitales, etc.

- Gran sincronía con procesos externos.

- Gran aceptación en el campo del Procesamiento Digital de Señales y las Comunicaciones.

Dentro de este grupo de conversores A/D, encontramos los conversores Flash, dos pasos (*Two step*), Subrango (*Subranging*), Doblaje (*Folding*), Interpolación (*Interpoling*) y *Pipeline*. Los conversores A/D con los que cuentan los sistemas empleados para la realización de la presente tesis son tipo *Pipeline*, como se verá en el capítulo siguiente.

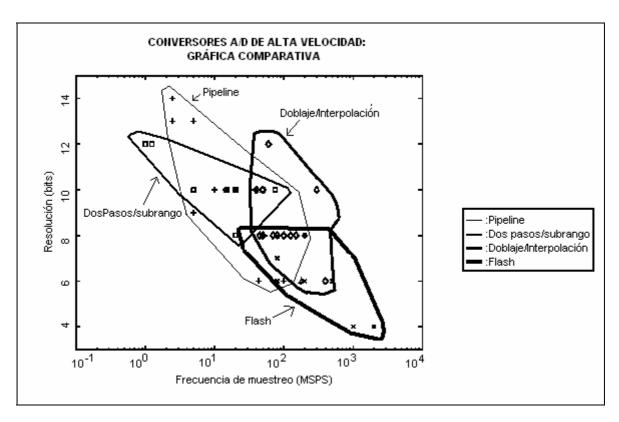

Una gráfica comparativa entre los conversores de alta velocidad se muestra a continuación en la Figura 2.23. En dicha gráfica, se denota la relación existente entre la resolución en bits entregada por este tipo de conversores y la tasa de muestreo a la que trabajan.

\_

<sup>&</sup>lt;sup>4</sup> Referencia Bibliográfica: [14]

Figura 2.23: Comparación entre distintos tipos de conversores A/D de alta velocidad, [14].

En la figura presentada, los conversores de dos pasos y de subrango, son agrupados debido a su similitud en operación y diseño. Sucede de igual manera con los conversores de Doblaje e Interpolación.

De acuerdo con la Figura 2.23, puede observarse que existe una tendencia a diseñar conversores de alta velocidad aunque posean poca resolución; a diferencia de tiempos anteriores en donde se preferían conversores de buena resolución pero con una limitada velocidad de muestreo. Mientras que los conversores *Pipeline* dominan la resolución en bajas frecuencias de entrada, los conversores tipo *Flash* lo hacen a altas frecuencias. Los conversores de dos pasos y subrango así como los de Doblaje e Interpolación caen en un rango intermedio.

Esta tendencia existente en el diseño de conversores A/D de alta velocidad representa una línea a seguir dentro del Procesamiento Digital de Señales; en este sentido, todas aquellas funciones que requieren una resolución o velocidad de procesamiento mayor que las que otorgan los actuales conversores A/D, deben ser realizados en el dominio analógico. Se ha observado en años recientes, que existe un proceso de desarrollo tecnológico en este sentido que abarca periodos de 4 años, es decir, aproximadamente cada 4 años surgen mejoras en el diseño e implementación de conversores A/D de alta velocidad. Un estimado sugiere que para una resolución

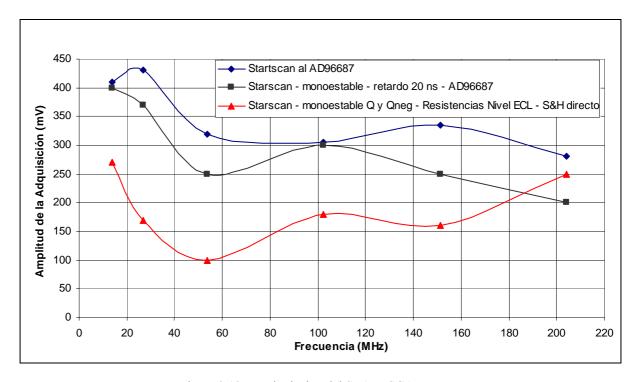

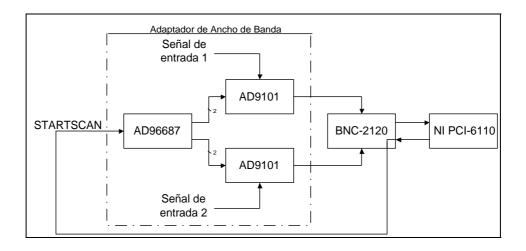

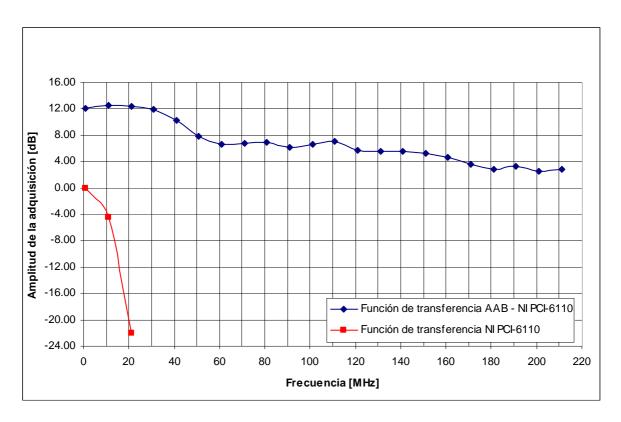

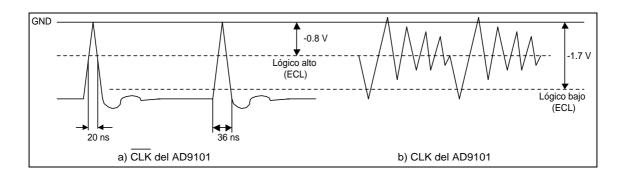

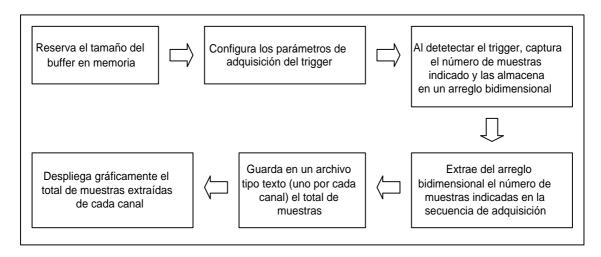

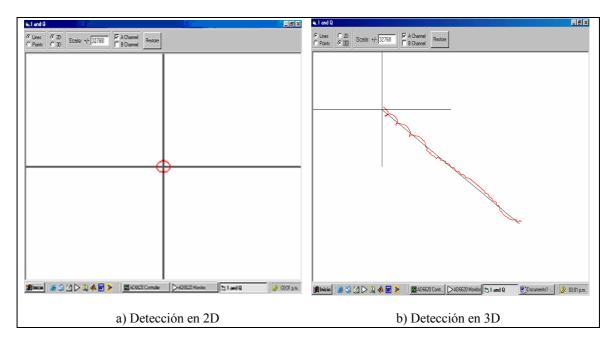

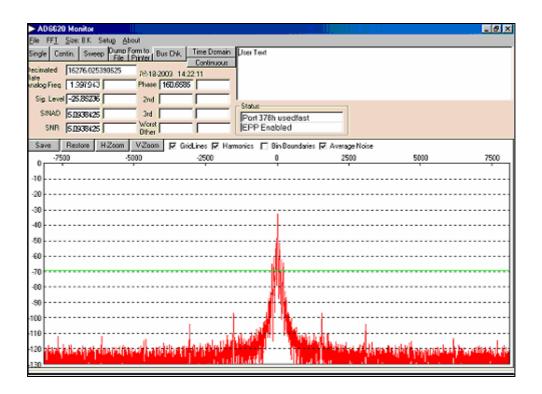

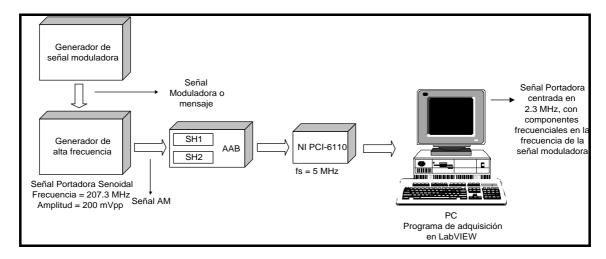

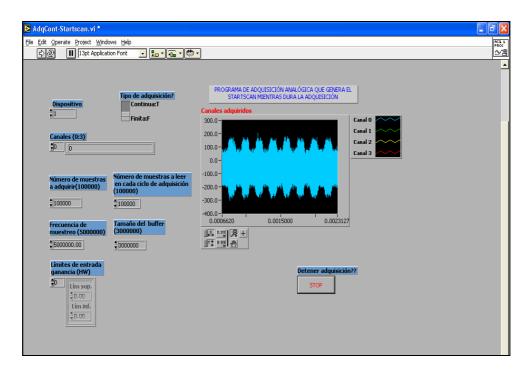

específica, la velocidad de muestreo fs se ve incrementada en un 50% cada 4 años, de la misma forma, la resolución se incrementa en promedio medio bit en este mismo periodo de tiempo.