## Apéndice A Hojas de especificaciones

## 1. Introduction

CII51001-3.2

## Introduction

Following the immensely successful first-generation Cyclone<sup>®</sup> device family, Altera® Cyclone II FPGAs extend the low-cost FPGA density range to 68,416 logic elements (LEs) and provide up to 622 usable I/O pins and up to 1.1 Mbits of embedded memory. Cyclone II FPGAs are manufactured on 300-mm wafers using TSMC's 90-nm low-k dielectric process to ensure rapid availability and low cost. By minimizing silicon area, Cyclone II devices can support complex digital systems on a single chip at a cost that rivals that of ASICs. Unlike other FPGA vendors who compromise power consumption and performance for low-cost, Altera's latest generation of low-cost FPGAs—Cyclone II FPGAs, offer 60% higher performance and half the power consumption of competing 90-nm FPGAs. The low cost and optimized feature set of Cyclone II FPGAs make them ideal solutions for a wide array of automotive, consumer, communications, video processing, test and measurement, and other end-market solutions. Reference designs, system diagrams, and IP, found at www.altera.com, are available to help you rapidly develop complete end-market solutions using Cyclone II FPGAs.

## **Low-Cost Embedded Processing Solutions**

Cyclone II devices support the Nios II embedded processor which allows you to implement custom-fit embedded processing solutions. Cyclone II devices can also expand the peripheral set, memory, I/O, or performance of embedded processors. Single or multiple Nios II embedded processors can be designed into a Cyclone II device to provide additional co-processing power or even replace existing embedded processors in your system. Using Cyclone II and Nios II together allow for low-cost, high-performance embedded processing solutions, which allow you to extend your product's life cycle and improve time to market over standard product solutions.

### Low-Cost DSP Solutions

Use Cyclone II FPGAs alone or as DSP co-processors to improve price-to-performance ratios for digital signal processing (DSP) applications. You can implement high-performance yet low-cost DSP systems with the following Cyclone II features and design support:

- Up to 150 18 × 18 multipliers

- Up to 1.1 Mbit of on-chip embedded memory

- High-speed interfaces to external memory

- DSP intellectual property (IP) cores

- DSP Builder interface to The Mathworks Simulink and Matlab design environment

- DSP Development Kit, Cyclone II Edition

Cyclone II devices include a powerful FPGA feature set optimized for low-cost applications including a wide range of density, memory, embedded multiplier, and packaging options. Cyclone II devices support a wide range of common external memory interfaces and I/O protocols required in low-cost applications. Parameterizable IP cores from Altera and partners make using Cyclone II interfaces and protocols fast and easy.

## **Features**

The Cyclone II device family offers the following features:

- High-density architecture with 4,608 to 68,416 LEs

- M4K embedded memory blocks

- Up to 1.1 Mbits of RAM available without reducing available logic

- 4,096 memory bits per block (4,608 bits per block including 512 parity bits)

- Variable port configurations of  $\times 1$ ,  $\times 2$ ,  $\times 4$ ,  $\times 8$ ,  $\times 9$ ,  $\times 16$ ,  $\times 18$ ,  $\times 32$ , and  $\times 36$

- True dual-port (one read and one write, two reads, or two writes) operation for  $\times 1$ ,  $\times 2$ ,  $\times 4$ ,  $\times 8$ ,  $\times 9$ ,  $\times 16$ , and  $\times 18$  modes

- Byte enables for data input masking during writes

- Up to 260-MHz operation

- Embedded multipliers

- Up to 150 18- × 18-bit multipliers are each configurable as two independent 9- × 9-bit multipliers with up to 250-MHz performance

- Optional input and output registers

- Advanced I/O support

- High-speed differential I/O standard support, including LVDS, RSDS, mini-LVDS, LVPECL, differential HSTL, and differential SSTL

- Single-ended I/O standard support, including 2.5-V and 1.8-V, SSTL class I and II, 1.8-V and 1.5-V HSTL class I and II, 3.3-V PCI and PCI-X 1.0, 3.3-, 2.5-, 1.8-, and 1.5-V LVCMOS, and 3.3-, 2.5-, and 1.8-V LVTTL

- Peripheral Component Interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 3.0* compliance for 3.3-V operation at 33 or 66 MHz for 32- or 64-bit interfaces

- PCI Express with an external TI PHY and an Altera PCI Express ×1 Megacore<sup>®</sup> function

- 133-MHz PCI-X 1.0 specification compatibility

- High-speed external memory support, including DDR, DDR2, and SDR SDRAM, and QDRII SRAM supported by drop in Altera IP MegaCore functions for ease of use

- Three dedicated registers per I/O element (IOE): one input register, one output register, and one output-enable register

- Programmable bus-hold feature

- Programmable output drive strength feature

- Programmable delays from the pin to the IOE or logic array

- I/O bank grouping for unique VCCIO and/or VREF bank settings

- MultiVolt<sup>™</sup> I/O standard support for 1.5-, 1.8-, 2.5-, and 3.3-interfaces

- Hot-socketing operation support

- Tri-state with weak pull-up on I/O pins before and during configuration

- Programmable open-drain outputs

- Series on-chip termination support

### Flexible clock management circuitry

- Hierarchical clock network for up to 402.5-MHz performance

- Up to four PLLs per device provide clock multiplication and division, phase shifting, programmable duty cycle, and external clock outputs, allowing system-level clock management and skew control

- Up to 16 global clock lines in the global clock network that drive throughout the entire device

### Device configuration

- Fast serial configuration allows configuration times less than 100 ms

- Decompression feature allows for smaller programming file storage and faster configuration times

- Supports multiple configuration modes: active serial, passive serial, and JTAG-based configuration

- Supports configuration through low-cost serial configuration devices

- Device configuration supports multiple voltages (either 3.3, 2.5, or 1.8 V)

### Intellectual property

Altera megafunction and Altera MegaCore function support, and Altera Megafunctions Partners Program (AMPP<sup>SM</sup>) megafunction support, for a wide range of embedded processors, on-chip and off-chip interfaces, peripheral functions, DSP functions, and communications functions and

protocols. Visit the Altera IPMegaStore at www.altera.com to download IP MegaCore functions.

• Nios II Embedded Processor support

The Cyclone II family offers devices with the Fast-On feature, which offers a faster power-on-reset (POR) time. Devices that support the Fast-On feature are designated with an "A" in the device ordering code. For example, EP2C5A, EP2C8A, EP2C15A, and EP2C20A. The EP2C5A is only available in the automotive speed grade. The EP2C8A and EP2C20A are only available in the industrial speed grade. The EP2C15A is only available with the Fast-On feature and is available in both commercial and industrial grades. The Cyclone II "A" devices are identical in feature set and functionality to the non-A devices except for support of the faster POR time.

Cyclone II A devices are offered in automotive speed grade. For more information, refer to the Cyclone II section in the *Automotive-Grade Device Handbook*.

For more information on POR time specifications for Cyclone II A and non-A devices, refer to the *Hot Socketing & Power-On Reset* chapter in the *Cyclone II Device Handbook*.

Table 1–1 lists the Cyclone II device family features. Table 1–2 lists the Cyclone II device package offerings and maximum user I/O pins.

| Table 1–1. Cyclone II FPGA Family Features (Part 1 of 2) |           |           |            |            |         |         |               |

|----------------------------------------------------------|-----------|-----------|------------|------------|---------|---------|---------------|

| Feature                                                  | EP2C5 (2) | EP2C8 (2) | EP2C15 (1) | EP2C20 (2) | EP2C35  | EP2C50  | EP2C70        |

| LEs                                                      | 4,608     | 8,256     | 14,448     | 18,752     | 33,216  | 50,528  | 68,416        |

| M4K RAM blocks (4<br>Kbits plus<br>512 parity bits       | 26        | 36        | 52         | 52         | 105     | 129     | 250           |

| Total RAM bits                                           | 119,808   | 165,888   | 239,616    | 239,616    | 483,840 | 594,432 | 1,152,00<br>0 |

| Embedded multipliers (3)                                 | 13        | 18        | 26         | 26         | 35      | 86      | 150           |

| PLLs                                                     | 2         | 2         | 4          | 4          | 4       | 4       | 4             |

| Table 1–1. Cyclone II FPGA Family Features (Part 2 of 2) |                  |           |            |                   |        |        |        |

|----------------------------------------------------------|------------------|-----------|------------|-------------------|--------|--------|--------|

| Feature                                                  | <b>EP2C5</b> (2) | EP2C8 (2) | EP2C15 (1) | <b>EP2C20</b> (2) | EP2C35 | EP2C50 | EP2C70 |

| Maximum user I/O pins                                    | 158              | 182       | 315        | 315               | 475    | 450    | 622    |

### *Notes to Table 1–1:*

- (1) The EP2C15A is only available with the Fast On feature, which offers a faster POR time. This device is available in both commercial and industrial grade.

- (2) The EP2C5, EP2C8, and EP2C20 optionally support the Fast On feature, which is designated with an "A" in the device ordering code. The EP2C5A is only available in the automotive speed grade. The EP2C8A and EP2C20A devices are only available in industrial grade.

- (3) This is the total number of  $18 \times 18$  multipliers. For the total number of  $9 \times 9$  multipliers per device, multiply the total number of  $18 \times 18$  multipliers by 2.

## MC33178, MC33179

## Low Power, Low Noise Operational Amplifiers

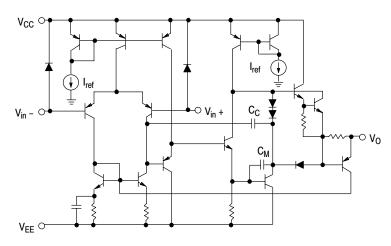

The MC33178/9 series is a family of high quality monolithic amplifiers employing Bipolar technology with innovative high performance concepts for quality audio and data signal processing applications. This device family incorporates the use of high frequency PNP input transistors to produce amplifiers exhibiting low input offset voltage, noise and distortion. In addition, the amplifier provides high output current drive capability while consuming only  $420\,\mu\text{A}$  of drain current per amplifier. The NPN output stage used, exhibits no deadband crossover distortion, large output voltage swing, excellent phase and gain margins, low open–loop high frequency output impedance, symmetrical source and sink AC frequency performance.

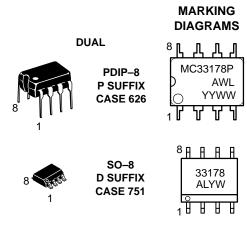

The MC33178/9 family offers both dual and quad amplifier versions, tested over the vehicular temperature range, and are available in DIP and SOIC packages.

- 600 Ω Output Drive Capability

- Large Output Voltage Swing

- Low Offset Voltage: 0.15 mV (Mean)

- Low T.C. of Input Offset Voltage:  $2.0 \mu V/^{\circ}C$

- Low Total Harmonic Distortion: 0.0024%

(@ 1.0 kHz w/600 Ω Load)

- High Gain Bandwidth: 5.0 MHz

- High Slew Rate: 2.0 V/µs

- Dual Supply Operation: ±2.0 V to ±18 V

- ESD Clamps on the Inputs Increase Ruggedness without Affecting Device Performance

Figure 1. Representative Schematic Diagram (Each Amplifier)

### ON Semiconductor™

### http://onsemi.com

QUAD

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

### ORDERING INFORMATION

| Device     | Package | Shipping         |  |

|------------|---------|------------------|--|

| MC33178D   | SO-8    | 98 Units/Rail    |  |

| MC33178DR2 | SO-8    | 2500 Tape & Reel |  |

| MC33178P   | PDIP-8  | 50 Units/Rail    |  |

| MC33179D   | SO-14   | 55 Units/Rail    |  |

| MC33179DR2 | SO-14   | 2500 Tape & Reel |  |

| MC33179P   | PDIP-14 | 25 Units/Rail    |  |

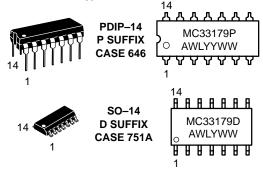

# LM111/LM211/LM311 Voltage Comparator

## 1.0 General Description

The LM111, LM211 and LM311 are voltage comparators that have input currents nearly a thousand times lower than devices like the LM106 or LM710. They are also designed to operate over a wider range of supply voltages: from standard ±15V op amp supplies down to the single 5V supply used for IC logic. Their output is compatible with RTL, DTL and TTL as well as MOS circuits. Further, they can drive lamps or relays, switching voltages up to 50V at currents as high as 50 mA.

Both the inputs and the outputs of the LM111, LM211 or the LM311 can be isolated from system ground, and the output can drive loads referred to ground, the positive supply or the negative supply. Offset balancing and strobe capability are provided and outputs can be wire OR'ed. Although slower than the LM106 and LM710 (200 ns response time vs 40 ns)

the devices are also much less prone to spurious oscillations. The LM111 has the same pin configuration as the LM106 and LM710.

The LM211 is identical to the LM111, except that its performance is specified over a  $-25^{\circ}$ C to  $+85^{\circ}$ C temperature range instead of  $-55^{\circ}$ C to  $+125^{\circ}$ C. The LM311 has a temperature range of  $0^{\circ}$ C to  $+70^{\circ}$ C.

### 2.0 Features

- Operates from single 5V supply

- Input current: 150 nA max. over temperature

- Offset current: 20 nA max. over temperature

- Differential input voltage range: ±30V

- Power consumption: 135 mW at ±15V

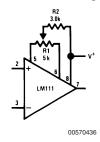

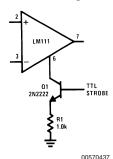

### 3.0 Typical Applications (Note 3)

### Offset Balancing

### Strobing

**Note:** Do Not Ground Strobe Pin. Output is turned off when current is pulled from Strobe Pin.

### Increasing Input Stage Current (Note 1)

00570438

Note 1: Increases typical common mode slew from 7.0V/µs to 18V/µs.

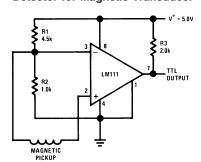

### **Detector for Magnetic Transducer**

00570439

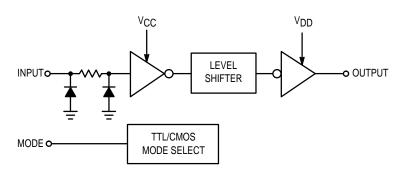

# Hex Level Shifter for TTL to CMOS or CMOS to CMOS

The MC14504B is a hex non-inverting level shifter using CMOS technology. The level shifter will shift a TTL signal to CMOS logic levels for any CMOS supply voltage between 5 and 15 volts. A control input also allows interface from CMOS to CMOS at one logic level to another logic level: Either up or down level translating is accomplished by selection of power supply levels VDD and VCC. The VCC level sets the input signal levels while VDD selects the output voltage levels.

- UP Translates from a Low to a High Voltage or DOWN Translates from a High to a Low Voltage

- · Input Threshold Can Be Shifted for TTL Compatibility

- No Sequencing Required on Power Supplies or Inputs for Power Up or Power Down

- 3 to 18 Vdc Operation for VDD and VCC

- Diode Protected Inputs to VSS

- Capable of Driving Two Low–Power TTL Loads or One Low–Power Schottky TTL Load Over the Rated Temperature Range

### **LOGIC DIAGRAM**

| Mode Select          | Input Logic<br>Levels | Output Logic<br>Levels |

|----------------------|-----------------------|------------------------|

| 1 (V <sub>CC</sub> ) | TTL                   | CMOS                   |

| 0 (V <sub>SS</sub> ) | CMOS                  | CMOS                   |

1/6 of package shown.

## MC14504B

L SUFFIX CERAMIC CASE 620

P SUFFIX PLASTIC CASE 648

D SUFFIX SOIC CASE 751B

### **ORDERING INFORMATION**

MC14XXXBCP Plastic MC14XXXBCL Ceramic MC14XXXBD SOIC

$T_A = -55^{\circ}$  to 125°C for all packages.

#### **PIN ASSIGNMENT** VCC 16 🛮 עח 15 | F<sub>out</sub> A<sub>out</sub> 14 | Fin Ain [ 13 MODE Bout [ Bin [ 12 | E<sub>OUt</sub> □ Ein Cout [ 11 10 Dout Cin [ 9 🛭 D<sub>in</sub> V<sub>SS</sub> [

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields referenced to the VSS pin, only. Extra precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation, the ranges VSS  $\leq$  Vin  $\leq$  18 V and VSS  $\leq$  Vout  $\leq$  VDD are recommended.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD). Unused outputs must be left open.