### FACULTAD DE INGENIERIA U.N.A.M. DIVISION DE EDUCACION CONTINUA

#### A LOS ASISTENTES A LOS CURSOS

Las autoridades de la Facultad de Ingeniería, por conducto del jefe de la División de Educación Continua, otorgan una constancia de asistencia a quienes cumplan con los requisitos establecidos para cada curso.

El control de asistencia se llevará a cabo a través de la persona que le entregó las notas. Las inasistencias serán computadas por las autoridades de la División, con el fin de entregarle constancia solamente a los alumnos que tengan un mínimo de 80% de asistencias.

Pedimos a los asistentes recoger su constancia el día de la clausura. Estas se retendrán por el periodo de un año, pasado este tiempo la DECFI no se hará responsable de este documento.

Se recomienda a los asistentes participar activamente con sus ideas y experiencias, pues los cursos que ofrece la División están planeados para que los profesores expongan una tesis, pero sobre todo, para que coordinen las opiniones de todos los interesados, constituyendo verdaderos seminarios.

٤

Es muy importante que todos los asistentes llenen y entreguen su hoja de inscripción al inicio del curso, información que servirá para integrar un directorio de asistentes, que se entregará oportunamente.

Con el objeto de mejorar los servicios que la División de Educación Continua ofrece, al final del curso deberán entregar la evaluación a través de un cuestionario diseñado para emitir juicios anónimos.

Se recomienda llenar dicha evaluación conforme los profesores impartan sus clases, a efecto de no llenar en la última sesión las evaluaciones y con esto sean más fehacientes sus apreciaciones.

Atentamente División de Educación Continua.

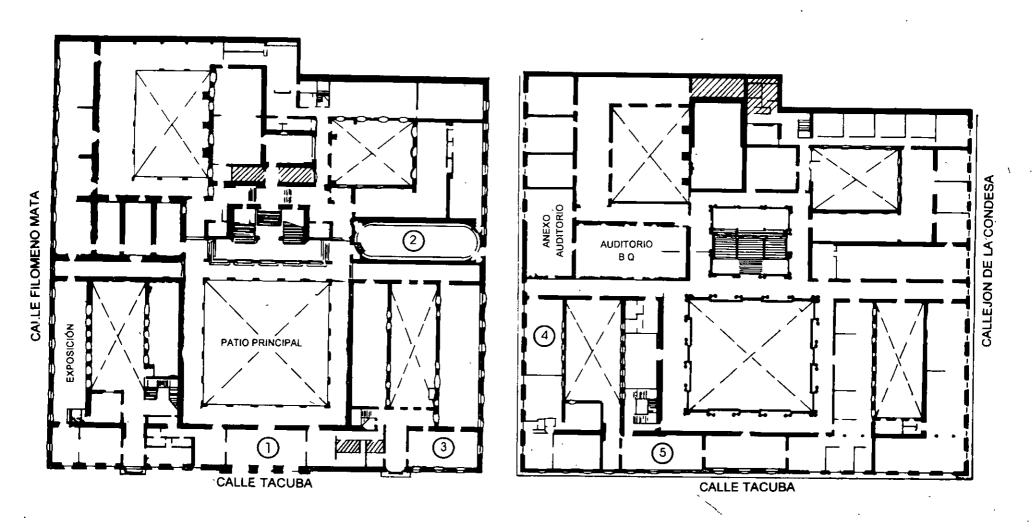

## PALACIO DE MINERIA

**PLANTA BAJA**

**MEZZANINNE**

## PALACIO DE MINERIA

Ier. PISO

## GUÍA DE LOCALIZACIÓN

- 1. ACCESO

- 2. BIBLIOTECA HISTÓRICA

- 3. LIBRERÍA UNAM

- 4. CENTRO DE INFORMACIÓN Y DOCUMENTACIÓN "ING. BRUNO MASCANZONI"

- 5. PROGRAMA DE APOYO A LA TITULACIÓN

- 6. OFICINAS GENERALES

- 7. ENTREGA DE MATERIAL Y CONTROL DE ASISTENCIA

- 8. SALA DE DESCANSO

**SANITARIOS**

AULAS

DIVISIÓN DE EDUCACIÓN CONTINUA FACULTAD DE INGENIERÍA U.N.A.M. CURSOS ABIERTOS

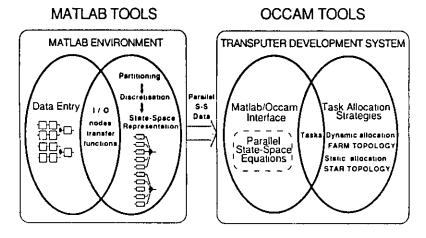

## Procesamiento Paralelo en Sistemas de Tiempo Real

División de Educación Continua de la Facultad de Ingeniería

en colaboración con el

Instituto de Investigaciones en Matemáticas Aplicadas y en Sistemas

Dr. Fabián García Nocetti

Dr. Julio Solano González

- 5. Lenguaje Occam

- 5.1 Primitivas

- 5.2 Constructores y Replicadores

- 5.3 Operadores y Arreglos

- 5.4 Funciones y Procedimientos

- 5.5 Protocolos de Comunicación

- 5.6 Timers y Puertos

- 6. Programación de Procesos Paralelos

- 6.1 Metodología

- 6.2 Programación en un procesador

- 6.3 Programación en múltiples procesadores

- 6.4 Configuración de programas

- 6.5 Mapeo de procesos en procesadores

- 6.6 Casos de estudio

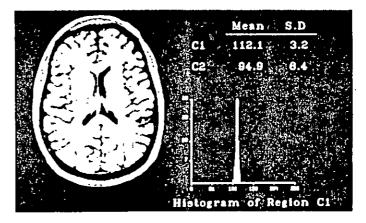

- 7. Aplicaciones .

- 7.1 Control

- 7.2 Robótica

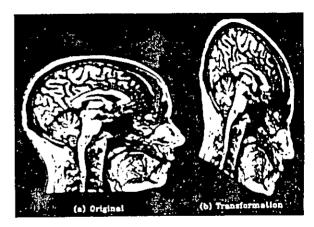

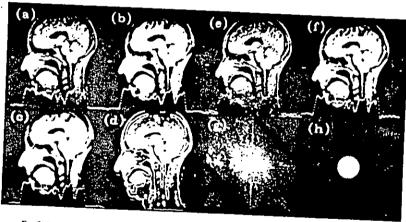

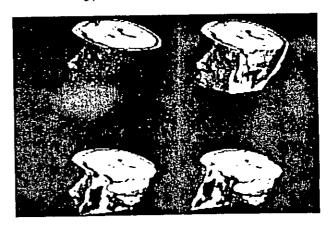

- 7.3 Procesamiento de Señales e Imágenes

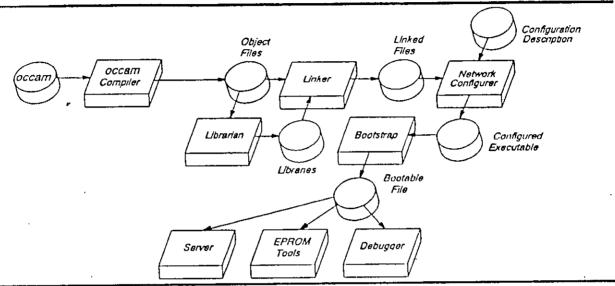

Apéndice. Occam 2 Toolset

#### TECNICAS DE ENSEÑANZA

Las sesiones teóricas estarán complementadas con lecturas relativas a los temas tratados y con ejercicios prácticos de programación paralela. Para desarrollar el trabajo práctico se utilizará una plataforma multiususario de procesamiento paralelo, accesible via red local. Este sistema está integrado por 16 transputers y cuenta con compiladores paralelos y herramientas de software.

#### BIBLIOGRAFIA

Stone, H.S., "High Performance Computer Architectures", Addison Wesley, 1987.

Krishnamurthy, E.V., "Parallel Processing Principles and Practice", Addison Wesley, 1989.

Bertsekas, D.P., "Parallel and Distributed Computation-Numerical Methods", Prentice Hall, 1989.

Pountain, D., May, D.; "A Tutorial Introduction to Occam Programming", Blackwell Publications, 1987.

Jones, G., Goldsmith, M., "Programming in Occam 2", Prentice Hall, 1988.

Harp, G., "Transputer Applications", Computer Systems Series, Pitman, 1989.

May, M.D., "Networks, Routers and Transputers -Function, Performance and Applications, IOS Press, 1993.

Thoeni, U., "Programming Real-Time Multicomputers for Signal Processing", Prentice Hall, 1994.

Russ, J.C., "The Image Processing Handbook -2nd. Edition", CRC Press, 1995.

Webber, H.C., "Image Processing and Transputers", IOS Press, 1992.

## 1

# Procesamiento Paralelo

#### PROCESAMIENTO PARALELO, TRANSPUTERS Y OCCAM

#### DR. FABIAN GARCIA NOCETTI DR. JULIO SOLANO GONZALEZ

Laboratorio de Procesamiento Paralelo

Departamento de Electrónica y Automatización

Instituto de Investigaciones en Matemáticas Aplicadas y en Sistemas

Universidad Nacional Autónoma de México

Apdo. Postal 20-726 Admon. 20, Delegación Alvaro Obregón

01000 México D.F.

#### 1. INTRODUCCION.

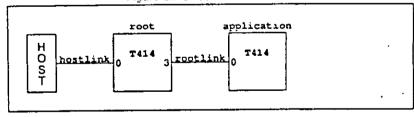

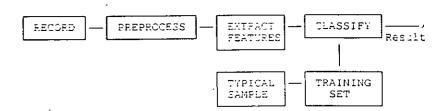

Los sistemas convencionales de cómputo operan en una forma secuencial, en donde las instrucciones de un programa son ejecutadas una a la vez. Esta característica ha sido forzada por la arquitectura secuencial de computadoras convencionales (arquitectura von Neumann), en la cual un procesador central esta conectado a un banco de memoria por medio de un bus. Desde entonces la mayoría de sucesivas generaciones de computadoras disponibles han seguido este diseño [1]. Sin embargo una gran variedad de problemas asociados a las áreas de control, visión, simulación, procesamiento de voz, imágenes y procesamiento digital de señales poseen un paralelismo intrínseco. De hecho el resolver este tipo de problemas en forma secuencial ha sido computacionalmente intensivo y restrictivo, sobre todo cuando se trata con aplicaciones en tiempo real, en donde se manejan intervalos de muestreo muy cortos del orden de milisegundos.

Un caso típico en ingeniería de control es la implementación de un controlador digital en tiempo real, en donde el cálculo de las variables controladas debe ser realizado dentro de un intervalo de muestreo típico de 5-20 ms [2]. Aun considerando el poder de cómputo de modernos procesadores secuenciales convencionales, esto puede ser dificil de alcanzar, sobre todo cuando se manejan múltiples variables. Ya que este tipo de sistemas puede envolver típicamente, un número de algoritmos de control, simulación, optimización, filtrado e identificación, junto con otras actividades como adquisición y chequeo de información. Claramente, a mayor complejidad de los algoritmos corresponde una mayor dificultad en el problema de realizar los cálculos necesarios en tiempo-real.

Aplicaciones diferentes imponen demandas variables en el controlador. Por ejemplo, los intervalos de muestreo para el control de motores eléctricos deben ser cortos debido a las pequeñas constantes de tiempo manejadas. Sistemas multivariables, envuelven un mayor nivel de complejidad en el cálculo de las señales controladas ya que estas deben ser calculadas simultáneamente [3]. En sistemas de seguridad, donde la confiabilidad es fundamental, la incorporación de características adicionales tales como tolerancia de fallas y redundancia, se pueden traducir en un incremento considerable en la carga computacional.

Como se puede observar, ciertas aplicaciones reales están sobrepasando los límites de desempeño de arquitecturas convencionales [4]. Aunque el uso de la tecnología de integración ha traído como resultado un incremento en la velocidad de los procesadores y en consecuencia de los sistemas de cómputo, la tecnología no ha logrado incrementar la velocidad en la misma proporción que el nivel de integración. La velocidad máxima a la que las componentes electrónicas operan ha marcado un límite en el diseño de procesadores más veloces. La alternativa ha sido entonces modificar la arquitectura típica de los sistemas de cómputo. Esto ha estimulado la investigación y el uso de arquitecturas alternativas que satisfagan las nuevas demandas computacionales de una manera efectiva y práctica. Procesamiento paralelo ha sido una de las mas viables alternativas.

La disponibilidad actual de arquitecturas de procesamiento paralelo, que permiten distribuir tanto algoritmos como información sobre un número de procesadores, ha creado nuevas oportunidades para el diseño e implementación de sistemas más rápidos y complejos [5]. Procesamiento paralelo están siendo cada vez más atractivo como un medio para construir sistemas de alto desempeño y confiabilidad [6].

La manera convencional de lograr alto desempeño es mediante la partición del sistema en módulos y la distribución de éstos en un número adecuado de procesadores para lograr el menor tiempo de ejecución posible. Confiabilidad es llevada a cabo mediante el uso de tolerancia a fallas, que es la habilidad de un sistema para continuar operando en presencia de algún tipo de falla. La tecnología de cómputo paralelo de hecho ha teniendo un gran impacto en el diseño e implementación de sistemas en tiempo real asociados a problemas de control, visión, simulación, procesamiento de voz, imágenes y procesamiento digital de señales. Dicha tecnología ha expandido el dominio factible de este tipo de sistemas [7]. Especialmente en sistemas que operan en tiempo real y sistemas integrados, donde las limitaciones de procesamiento han restringido tradicionalmente sus capacidades.

En particular la introducción del transputer y su lenguaje asociado occam, para el soporte de procesamiento paralelo, ha tenido un gran impacto en un número de aplicaciones, permitiendo el diseño y construcción de sistemas más rápidos y complejos, de una forma simple y estructurada [8]. El transputer y occam, han sido diseñados específicamente para ser usados en sistemas de múltiples procesadores, y diversas topologías, ofreciendo el prospecto de un desempeño escalable a medida que más procesadores son agregados al sistema, siendo éste un factor determinante para su utilización en una creciente variedad de aplicaciones.

#### 2. PROCESAMIENTO PARALELO

#### 2.1 Beneficios de Procesamiento Paralelo

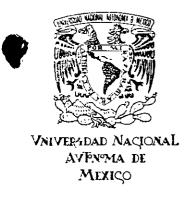

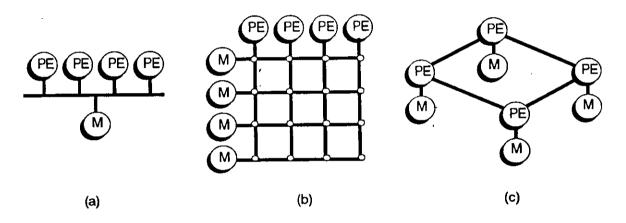

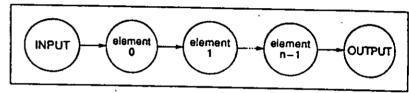

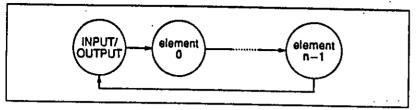

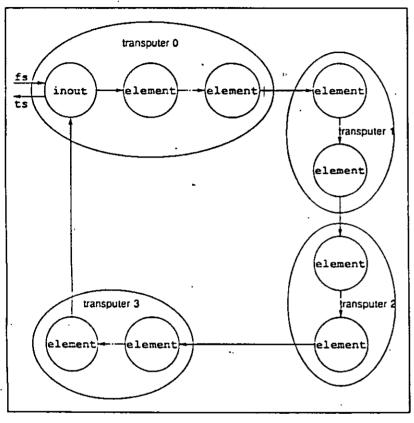

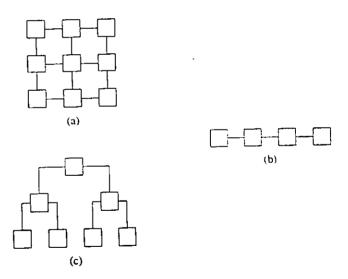

Un sistema de procesamiento paralelo esta compuesto por un número de elementos de procesamiento (PEs) que pueden operar en forma concurrente, comunicándose entre si cuando es necesario, Figura 1. Las diversas arquitecturas difieren entre si, tanto por el poder de cómputo de sus PEs como por su modo de conexión.

Figura 1. Sistema de Procesamiento Paralelo Generalizado.

Esto conduce a conceptos nuevos tales como granularidad de actividad, el cual es una medida del tamaño de las actividades que pueden ser ejecutadas efectivamente por los PEs de una 4 arquitectura específica. PEs de arquitecturas de grano fino son caracterizados por tener operaciones limitadas y específicas, así como un gran ancho de banda para comunicación de información. Por otro lado, PEs de arquitecturas de grano grande poseen operaciones y de propósito más general pero una banda más reducida de comunicación [9]. Ya ha sido señalado que a medida que una aplicación en tiempo real se torna más compleja, un procesador de propósito general resulta inadecuado para ejecutar las operaciones necesarias dentro del intervalo de muestreo requerido. El potencial ofrecido por un sistema de procesamiento paralelo, ofrece una solución viable tanto al problema de velocidad como complejidad. Otros beneficios incluyen, flexibilidad, conectividad y habilidad para reconfiguración, lo cual permite construir diseños de sistemas redundantes y tolerantes a fallas. Además partiendo del hecho que las operaciones concurrentes son un fenómeno natural en sistemas que operan en tiempo real, el uso de procesamiento paralelo habilita al diseñador de este tipo de sistemas a expresar claramente la variedad de actividades secuenciales y paralelas que serán realizadas por el sistema digital objetivo. Finalmente la escalabilidad de un sistema multiprocesador, permite una fácil expansión para acomodar crecientes requerimientos futuros.

#### 2.2 Arquitecturas de Procesamiento Paralelo.

Dentro de un sistema de procesamiento paralelo los procesadores pueden ser interconectados de diferentes maneras, dando lugar a una gran variedad de arquitecturas. Similarmente, una variedad de métodos han sido desarrollados para programar estos sistemas. Frecuentemente se tiende a agrupar estas arquitecturas en dos tipos: arquitecturas de memoria compartida (procesadores pueden accesar memoria común) y arquitecturas de memoria distribuida (cada procesador tiene su propia memoria). Sin embargo, una de las clasificaciones más utilizadas es aquella conocida como taxonomía de Flynn [10]. Esta taxonomía considera la arquitectura

tradicional von Neumann como un modelo Single Instruction-stream Single Data-stream (SISD) y a las arquitecturas de procesamiento paralelo como:

- 1. Multiple Instruction-stream Single Data-stream (MISD). Varios procesadores ejecutan simultáneamente diferentes instrucciones en un mismo grupo de datos.

- 2. Single Instruction-stream Multiple Data-stream (SIMD). Varios procesadores ejecutan simultaneamente la misma instrucción en múltiples grupos de datos.

- 3. Multiple Instruction-stream Multiple Data-stream (SIMD). En esta arquitectura cada procesador puede realizar diferentes instrucciones en diferentes datos.

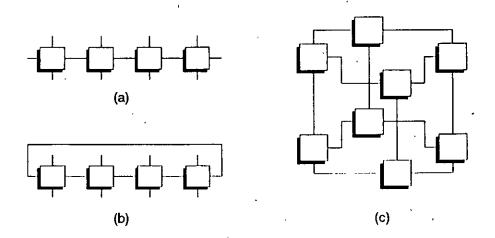

Este curso se ha centrado en arquitecturas del tipo MIMD realizadas con transputers, en donde cada uno de éstos puede ejecutar programas diferentes y se comunican entre sí solo para intercambiar resultados. Un número de topologías han sido derivadas de la implementación de este tipo de arquitecturas. La Figura 2, muestra algunas de las configuraciones mas utilizadas en la construcción de estos sistemas.

Figura 2. Configuraciones Típicas MIMD: (a)Bus Compartido; (b)Crossbar; (c)Punto PE = Elementos de Procesamiento; M = Memoria.

Los sistemas MIMD ofrecen una mayor flexibilidad que los sistemas SIMD y MISD, en el manejo de software de propósito general y han sido por tanto adoptados en la solución de problemas en un gran número de disciplinas. Sin embargo es conveniente notar que la implementación exitosa de un determinado algoritmo dependerá del grado de paralelismo que este ofrece, aunado a una adecuada selección de granularidad. El desempeño de un sistema de procesamiento paralelo es también dependiente de la relación conocida como R/C, donde R es el tiempo de ejecución de un proceso y C es el tiempo que ese proceso emplea en comunicaciones con otros procesos. Claramente un valor grande en esta relación es deseable.

Sin embargo no existe una regla definitiva para establecer un valor adecuado. Ya que valores grandes de R/C pueden ignorar paralelismo potencial en el problema, mientras que el subdividir el problema hasta alcanzar el máximo paralelismo, puede conducir a un exceso de

comunicaciones entre procesos. Por lo tanto, en la tarea de distribuir o mapear una aplicación en una arreglo de PEs, el diseñador debe seleccionar cuidadosamente la granularidad del algoritmo, de tal forma que mantenga una adecuada relación entre tiempos de ejecución y comunicación de los procesos que integran el sistema.

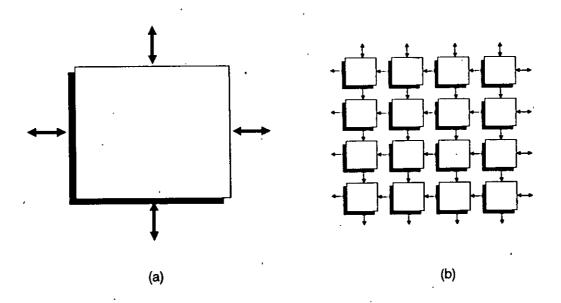

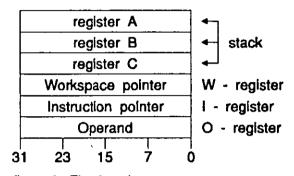

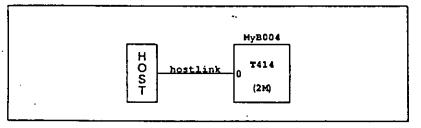

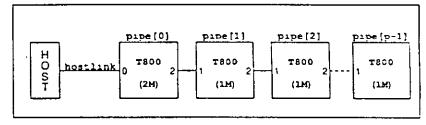

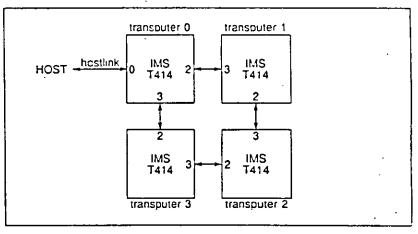

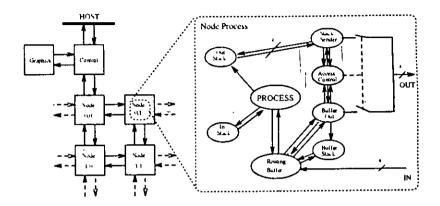

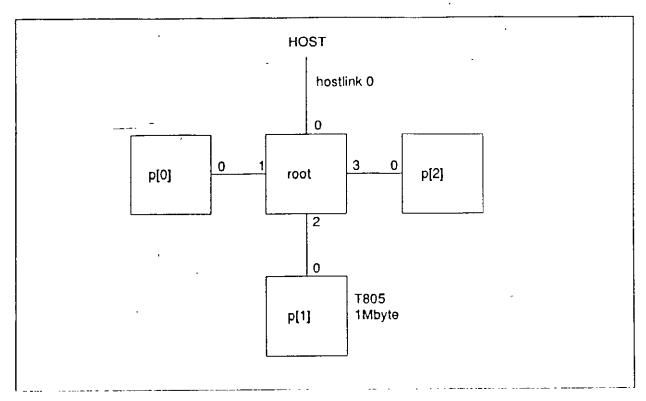

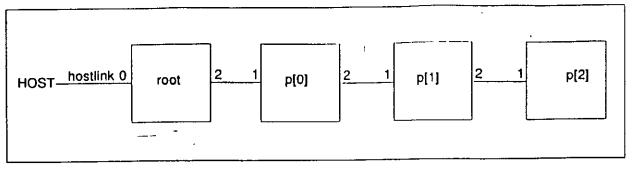

#### 3. TRANSPUTER Y OCCAM

El transputer es una arquitectura VLSI que soporta explícitamente concurrencia y sincronización [11]. La diferencia entre un transputer y una microcomputadora ordinaria, es que éste contiene un organizador de actividades "scheduler" integrado, capaz de distribuir su tiempo entre un número de procesos concurrentes, de esta forma el transputer, además de ejecutar procesos en modo secuencial, puede ejecutar procesos concurrentemente. Varios transputers se puede agrupar de una manera rápida y directa para formar redes y arreglos, ver Figura 3. Cada transputer trabaja en su propia actividad y usa su memoria local. Para que los transputers puedan cooperar en un sistema necesitan comunicarse entre si, esto es realizado a través de interfases seriales denominadas "links", cada uno con un canal de entrada y otro de salida.

Figura 3. (a) Un Transputer. (b) Una Red de Transputers.

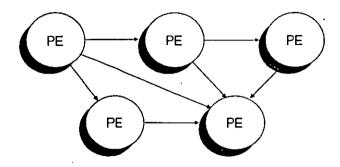

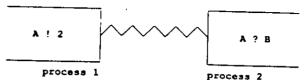

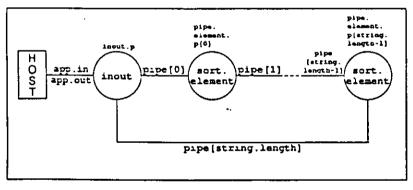

Por su parte el lenguaje occam esta diseñado para manejar tanto procesos secuenciales como concurrentes. Estos son modelados como procesos occam que trabajan con su propia información local. Un proceso coopera con otros procesos usando canales de comunicación. Una colección de procesos occam forma a su vez un proceso, de esta forma una jerarquía de procesos puede ser construida para modelar procesos reales.

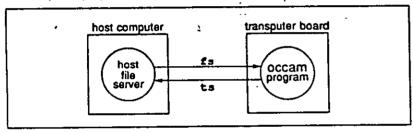

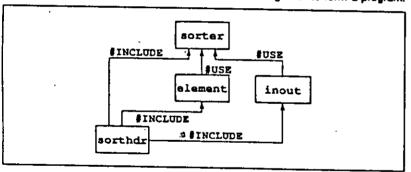

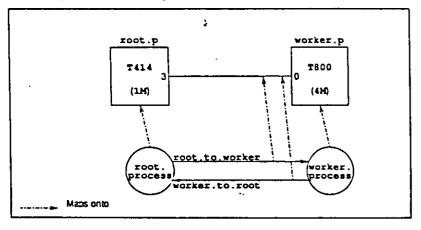

De acuerdo con lo anterior el modelo de proceso occam puede ser mapeado eficientemente en un arreglo de transputers, cada uno con su memoria local, comunicándose a través de links, ver Figura 4. Finalmente, no obstante su profunda asociación con el transputer, occam es un lenguaje de propósito general que puede ser implementado en otras arquitecturas. El transputer es considerado aquí como un vehículo eficiente para implementar este lenguaje.

Figura 4. Procesos Occam: (a) en un Transputer; (b) en varios Transputers.

#### 3.1 Arquitectura del Transputer

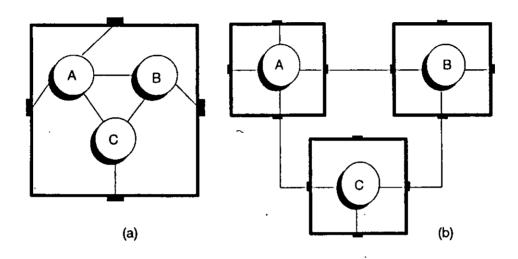

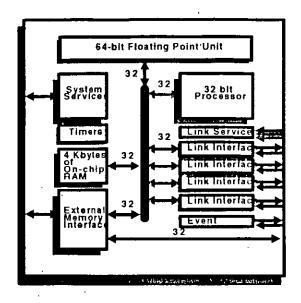

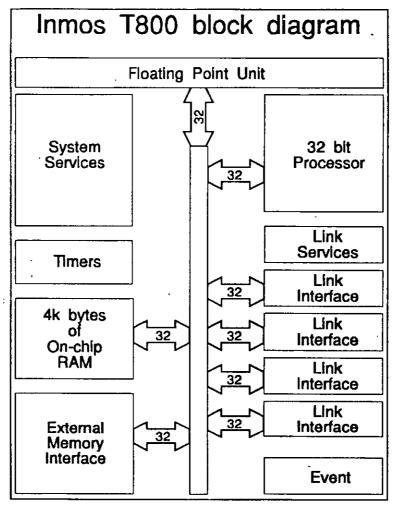

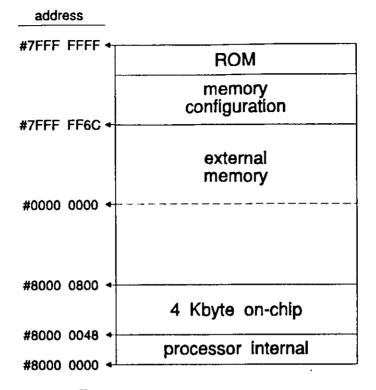

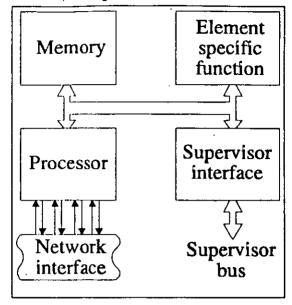

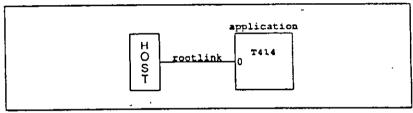

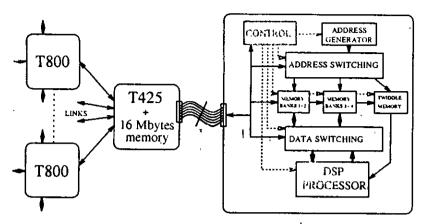

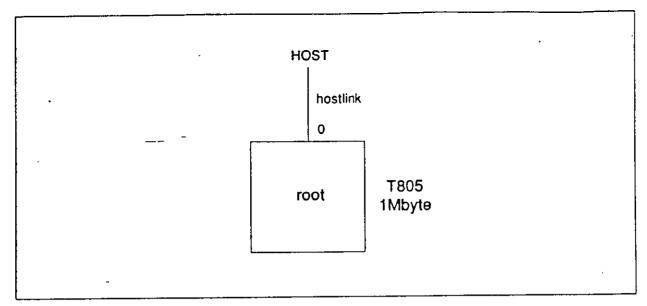

El transputer comprende una familia de microcomputadoras implementadas a nivel de VLSI, que incluyen, en un mismo circuito integrado, un procesador, memoria y links de comunicación, para interconectarse con otros transputers. La versión T800 del transputer es mostrada en la Figura 5.

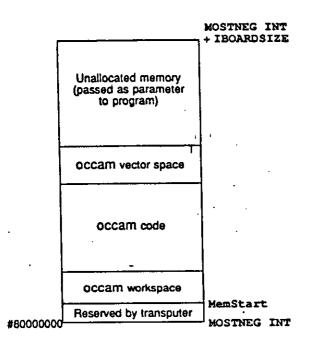

El transputer T800 consta de un procesador RISC de 32 bits (15 MIPS a 30 MHz), unidad de punto flotante de 64 bits (2.25 Mflops a 30 MHz), 4 Kbytes de memoria local RAM, una interfase configurable para accesar memoria externa y cuatro links de comunicación, que operan a velocidad máxima de 20 Mbits/s [12]. Además de las características típicas del transputer, relativas a integración, velocidad de operación e interfases, otro aspecto atractivo es su soporte de concurrencia. El desarrollo y evaluación de una aplicación, como un número de procesos concurrentes, puede llevarse a cabo enteramente en un solo transputer. Después, los procesos componentes de la misma aplicación pueden ser distribuidos para operar realmente en paralelo en una red de transputers. Lo anterior requiere de instrucciones occam adicionales de configuración o mapeo que asocian cada proceso a ser ejecutado con su correspondiente transputer.

Figura 5. Arquitectura del Transputer T800.

En la implementación de aplicaciones en tiempo real, generalmente el diseñador es responsable de este mapeo físico de procesos en procesadores. Aunque existen sistemas operativos que realizan el mapeo de aplicaciones en forma transparente al usuario, estos generalmente introducen una mayor carga computacional al sistema, siendo sólo adecuados en aplicaciones fuera de línea [13]. Diferentes topologías han sido utilizadas en aplicaciones de sistemas de transputers. Estas topologías incluyen procesadores en línea, anillo, árbol, arreglos de 2 dimensiones, hipercubos, etc. La Figura 6 muestra algunos de estos arreglos.

Figura 6. Topologías de Transputers: (a) Línea; (b) Anillo; (c) Hipercubo.

La nueva generación de transputers, serie T9000, actualmente en desarrollo, brindará un importante incremento en el desempeño de sistemas de procesamiento paralelo. Esta serie ofrece un arquitectura basada en procesadores "pipeline" (150 MIPS y 20 MFLOPS a 50 MHz), 16 Kbytes de memoria local y un nuevo sistema de comunicación operando a 100 Mbits/s [15]. Un aspecto también importante es que sus instrucciones son compatible con previas series, garantizando compatibilidad con sistemas de transputers actuales.

#### 3.2 El Lenguaje Occam

Transputers pueden ser programados en lenguajes de alto nivel (C, FORTRAN ó PASCAL), sin embargo cuando es necesario explotar concurrencia y ganar mayor beneficio de su arquitectura, occam es recomendado, ya que provee muchas de las ventajas de un lenguaje de alto nivel y al mismo tiempo una alta eficiencia (comparable con la de un ensamblador). Occam es un lenguaje de programación diseñado para manejar concurrencia [16]. Esto es relevante sobre todo en aplicaciones prácticas de paralelo, ya que permite expresar un sistema en términos de procesos concurrentes que se comunican entre sí, lo cual da una estructura simple y clara. Además, ofrece la alternativa de ejecutar todos los procesos en un solo transputer o distribuirlos en un número de éstos [17].

La unidad básica de programación en occam es el "proceso", un proceso empieza, realiza una serie de acciones y se detiene o termina. Este concepto puede parecer similar a otros conceptos de programación convencional, excepto que en occam puede haber mas de un proceso ejecutándose al mismo tiempo y tratando de comunicarse con algún otro a través de sus canales. Los procesos en occam están constituidos por tres procesos primitivos:

asignación v := e ; asigna el valor de la variable e a la variable v,

entrada -c?x ; ---recibe un-valor en el canal c, lo asigna a la variable x , y

salida c! e ; transmite el valor de la expresión e a través del canal c.

Cuando un comando de salida es encontrado en un proceso, este proceso se mantiene en ese estado hasta que otro proceso ejecuta el comando de entrada correspondiente. De tal forma que la comunicación se lleve a cabo en el canal común utilizado por ambos procesos. Del mismo modo un comando de entrada no puede ser ejecutado, hasta que el correspondiente comando de salida es alcanzado en el proceso contraparte. De esta forma se asegura la sincronización. Varios procesos primitivos pueden ser combinados en uno más grande y formar un *constructor*, que es a su vez un proceso y puede ser usado como componente de otro constructor. Estos son básicamente:

PAR -constructor paralelo, y

ALT -constructor alternativo

Constructores típicos tales como IF y WHILE son también soportados. Como occam es un lenguaje de programación concurrente, ejecución secuencial, paralela o alternativa debe ser especificada. El constructor SEQ indica que las declaraciones incluidas dentro del proceso serán ejecutadas en

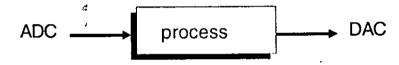

de programación concurrente, ejecución secuencial, paralela o alternativa debe ser especificada. El constructor SEQ indica que las declaraciones incluidas dentro del proceso serán ejecutadas en secuencia. En el siguiente proceso, una señal medida es leída en el canal ADC, escalada y el resultado es enviado al canal DAC:

**SEQ**

ADC ? señal.mediada señal.escalada \* factor

DACI -- -- 1 --- 1-1-

DAC! señal.escalada

Nótese que existe una sangria entre el constructor y sus procesos componentes. Figura 7 ilustra la relación entre este proceso y sus canales.

Figure 7. Ejemplo de Constructor Secuencial

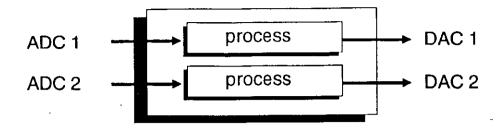

El constructor PAR establece que los procesos incluidos serán ejecutados en paralelo, ver Figura 8. Tomando como procesos componentes dos procesos secuenciales:

PAR

**SEQ**

ADC1? señal.mediada

señal.escalada := señal.escalada \* factor

DAC! señal.escalada

SEQ

ADC2 ? señal.mediada

señal.escalada := señal.escalada \* factor

DAC! señal.escalada

Figure 8. Ejemplo de Constructor Paralelo

El constructor ALT es usado para realizar la ejecución de procesos alternativos mediante la activación de su canal correspondiente. En el ejemplo: este constructor espera hasta que alguno de los canales de entrada canal1, canal2 ó canal3 es activado para realizar el proceso correspondiente. El constructor ejecuta el solamente el proceso asociado con la primera entrada que se lleve a cabo y finalmente termina. Ejemplo:

```

ALT

canal1 ? x

... proceso 1

canal2 ? x

... proceso 2

canal3 ? x

... proceso 3

```

Nótese que hemos usado la convención ... proceso para denotar el proceso que encierra esa declaración y expresar en forma mas clara el constructor. El constructor ALT ofrece un método formal de alto nivel para manejar eventos internos y externos que en procesadores convencionales son manejados como interrupciones a nivel de ensamblador.

#### 3.3 Programación en Tiempo Real

Prioridades son fundamentales en aplicaciones en tiempo real. Aunque occam ofrece soporte para establecer y asignar diferentes niveles de prioridad en la ejecución de procesos, en su implementación en el transputer solo existen dos niveles de prioridad (alta y baja), esto ha resultado insuficiente en diversos tipos aplicaciones de tiempo real, sin embargo se han desarrollado técnicas a nivel de programación que resuelven este problema a un costo computacional mínimo [18].

Occam además ofrece una manera directa de asignar procesos lógicos a procesadores físicos. El número de procesadores puede no corresponder al número de procesos, ya que es posible asignar varios procesos a un solo procesador. Es de hecho una buena práctica el descomponer el problema de tal forma que resulten más procesos que procesadores. Ya que es generalmente mas fácil agrupar procesos, que subdividirlos una vez que el diseño del sistema se ha establecido.

Existen dos formas fundamentales de asignar actividades a procesadores: estática y dinámica. En una asignación estática la asociación de actividades a el procesador es fija y se lleva a cabo antes de ejecutar el programa, mientras que en una asignación dinámica de actividades, éstas son distribuidas durante la ejecución del programa, de acuerdo a un número de criterios, tales como disponibilidad de procesadores, prioridades y dependencia de actividades.

La asignación dinámica de actividades ofrece un mayor potencial para una óptima utilización de procesadores, pero al mismo tiempo produce una disminución en el desempeño del sistema asociado con el incremento en el nivel de comunicaciones y el costo computacional del software de asignación y destribución. Lo cual puede ser inaceptable en cierto tipo de aplicaciones en tiempo real, en donde una asignación estática de actividades puede ofrecer un mejor desempeño.

#### **BIBLIOGRAFIA**

- 1. Kuck, D.J., "High Performance Computing", Oxford University Press, 1996.

- 2. García Nocetti, D.F. and Fleming, P.J. "Parallel Processing in Digital Control- Advances in Industrial Control", Springer-Verlag, 1992.

- 3. Stone, H.S., "High Performance Computer Architectures", Addison Wesley, 1987.

- 4 Krishnamurthy, E.V., "Parallel Processing Principles and Practice", Addison Wesley, 1989.

- 5. Thocni, U., "Programming Real-Time Multicomputers for Signal Processing", Prentice Hall, 1994.

- 6. Lewis, T. G., "Introduction to Parallel Computing", Prentice-Hall International, 1992.

- 7. Metropolis, N. and Rota, G.C. "A new Era in Computation", MIT Press, 1993.

- 8. Harp, G., "Transputer Applications", Computer Systems Series, Pitman, 1989.

- 9. Tzafestas, S. "Parallel and Distributed Computing in Engineering Systems", North-Holland, 1991.

- 10. Flynn, M.F., "Some Computer Organisations and Their Effectiveness", IEEE Trans Comput., C-21, 1972, pp. 948-960.

- 11. INMOS Limited, "Transputer Overview", The Transputer Databook, Second edition, 1989.

- 12. INMOS Limited, "Transputer T800", The Transputer Databook, Second edition, 1989.

- 13. Kim, T., "Operating Systems", in Transputer Applications (Ed. Harp, G.), Computer Systems Series, Pitman 1989.

- 14. May, M.D., Thompson, P.W., Welch, P.H., "Networks, Routers and Transputers -Function, Performance and Applications, IOS Press, 1993.

- 15. Dyson C., "The Next Generation Transputer", Technical Note, Inmos Bristol, July 1990.

- 16. Inmos Ltd, "Occam 2 Reference Manual", Prentice Hall, 1987.

- 17. Jones, G., Goldsmith, M., "Programming in Occam 2", Prentice Hall, 1988.

- 18. Welch, P.H. "Multi-Priority Schedulers for Transputer-based Real-time Control", Real-Time Systems with Transputers, IOS Press, 1990.

# Estructuras de Programación Paralela

### Chapter 11

## Approaches to writing parallel programs in occam

The previous chapters have concentrated on the various program constructs available in occam and have explained their use. In order to reap the most benefit from the use of occam and transputers, programs need to exhibit some degree of parallelism. Every application needs to be considered to see how the inherent parallelism may be best expressed and exploited. But this is not an easy exercise. The conventional mould of thinking and expressing the solution to a programming problem as a sequence of steps must be broken. A number of approaches for applying parallelism to problems have yielded promising results for occam and the transputer. However much more experience is needed in the art and science of parallel programming.

Parallelism is expressed within an occam program by parallel constructions. Given the fact that each parallel process may be mapped on to a separate processor for execution, the potential benefits in terms of speed and efficiency may be enormous. Nevertheless, efficiency considerations need to be taken into account so that the benefits gained from parallelism are not lost.

The granularity of the parallelism in the application and how it is distributed over a transputer network need to be carefully assessed. Granularity is a measure of parallelism - the number of parallel processes in an application. A large amount of parallelism is not necessarily an ideal situation. It is necessary to achieve a balance between keeping each processor busy with computation and maintaining inter-process communication time at a minimum. The current versions of the transputer do not provide message routing in hardware; valuable computation time can be taken up in providing extra occam processes to implement software message routing between processes. With a too fine-grained granularity, there will be many parallel processes and then the communications overhead can dominate the computation. However in coarse-grained granularity, with not so many parallel processes, the computation should dominate the communications.

The organisation of programs around the parallel paradigm has been approached in a number of different ways. These various approaches may be broadly classified into the following categories

algorithmic - quasi-independent tasks which execute sections of the problem solution algorithm (and are therefore non-identical), data and computed results being passed among the tasks as the algorithm dictates. • geometric - quasi-independent but identical tasks which process a portion of the data, and which interact with (or are affected by) neighbouring tasks, according to the geometry of the problem.

• process farming - fully independent but identical tasks which process the data in any order.

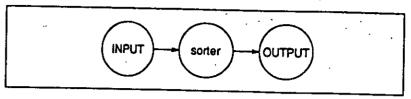

Analysis of the problem using data flow diagrams presents a graphical method for visualising the component processes of a program - the processes are represented by circles, the channels are represented by arcs connecting the circles. Such a method has been found useful in the design of occam programs [Kerridge]. Another graphical method which may also prove useful for designing occam programs is the Petri-net notation [Peterson]. This technique allows the graphical expression of parallel strands of computation, so that its suitability to the design of occam programs should be apparent. CSP [Hoare], the theoretical basis for occam, is an excellent tool for expressing the design of occam programs.

The following sections of the chapter discuss in more detail the three approaches to writing parallel programs in occam, giving a concrete example in each case. For simplicity of presentation, the handling of process termination has been omitted in the first two examples. Realistically, this should always be provided - see Chapter 6 for an example how this might be achieved. The third example contains code for process termination.

#### 11.1 Algorithmic parallelism

The algorithmic approach, also known as data flow decomposition, is concerned with injecting parallelism into the algorithm being used to solve the problem at hand. The algorithm may be an already existing sequential one or totally new. Parallelism can be introduced by considering how the algorithm may be broken up into separate, quasi-independent sections. Each section can then be executed in parallel, with data flowing between the sections as necessary. Each section will perform some computation with the data, and then pass the data on to the next section.

The inherent parallelism is frequently found in a loop or iteration. Consider a linear search for example. In the sequential case, each item in the list is compared one at a time as the search sequences through the list. This comparison may however be performed more efficiently in parallel - each comparison may be performed at the same time.

The algorithmic approach is modelled by occam parallel processes, each parallel process responsible for the execution of a section of the algorithm, using the synchronisation and communication provided by occam channels to transfer data between the processes. The communication overhead between the parallel processes in such circumstances can become

quite significant.

A common example of the algorithmic approach is the pipeline - each unit of the pipeline contributes by executing a section of the algorithm. The independent units may operate on separate portions of the data as the stream of data is fed down the pipeline. The overall effect of this overlapped operation is the realisation of parallel execution.

Such organisation is not limited to one-dimensional cases. For example, a systolic array is effectively a two-dimensional pipeline that may be used to great effect for the parallel execution of matrix operations [Jones and Goldsmith].

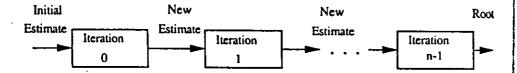

As an example of the algorithmic approach, consider the Newton-Raphson estimate technique for evaluating square-roots. This method starts off with the value of the number whose square-root is required and an initial estimate of the square-root. The Newton-Raphson formula is then applied in an iterative manner, each time producing a better estimate of the square-root from the previous value. If the iteration is performed a large number of times, the final estimate will be a close approximation to the real value.

The Newton-Raphson formula for calculating the square root of a number x is

$$y_{i+1} = \frac{1}{2}(y_i + \frac{x}{y_i})$$

where y<sub>i</sub>, y<sub>i+1</sub> are successive estimations of the root v.

This formula may be expressed in occam as

Estimate: - (Estimate + (Number / Estimate)) / 2.0 (REAL32)

where Number is the number whose square root is required and the initial value for Estimate is given. Usually, the initial value for Estimate is taken to be

Number / 2.0 (REAL32)

If the iteration is performed Iterations times, then a sequential solution may be written as

SEQ

Input? Number

Estimate := Number / 2.0 (REAL32)

SEQ Index - 0 FOR Iterations

Estimate := (Estimate + (Number / Estimate)) / 2.0 (REAL32)

Output! Estimate

```

Written in occam, this becomes

```

```

PROC Pipeline (CHAN OF REAL32 InPipe, OutPipe)

WHILE TRUE

REAL32 Number, Estimate:

SEQ

--- accept number and previous estimate

InPipe ? Number

InPipe ? Estimate

--- pass on number and new estimate

OutPipe! Number

OutPipe! (Estimate + (Number / Estimate)) / 2.0 (REAL32)

```

Finally, the Terminate process inputs the number and final estimate of the square root from the last pipeline process and outputs this value. Writing this in pseudo-code

```

WHILE data is available

SEQ

RECEIVE a number and final square root estimate from last pipeline process

OUTPUT this number and final estimate as results

```

In occam, this becomes

```

PROC Terminate (CHAN OF REAL32 Extract, Output)

WHILE TRUE

REAL32 Number, Root:

SEQ

-- extract number and root (final estimate) from pipeline

Extract? Number

Extract? Root

-- output results

```

Output! Number

Output! Root

PAR construction containing instances of In

The main process will comprise a PAR construction containing instances of *Initialise*, *Pipeline* and *Terminate*. The *Pipeline* process is replicated the desired number of times.

PAR

Initialise (InChan, Pipe [0])

PAR Index = 0 FOR Iterations

In IS Pipe [Index]:

Out IS Pipe [Index + 1]:

Pipeline (In, Out)

Terminate (Pipe [Iterations], OutChan)

The amounts of computation required for the sequential and parallel solutions are the same. However, the benefit derived by expressing the sequential algorithm as a parallel one accrues only when there are many numbers requiring the calculation of their square roots. The partial estimates for these numbers may all be within the pipeline at the same time (depending on the length of the pipeline) - each pipeline process can be calculating a different partial estimate. The automatic synchronisation of occam ensures the correct order of communication and, hence, the correct order of computation.

Other examples of the use of this approach are sorting [Pountain and May], prime number generating [Burns], systolic array processing [Jones and Goldsmith], compiling and solid modelling [May and Shepherd].

#### 11.2 Geometric parallelism

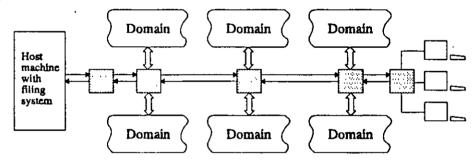

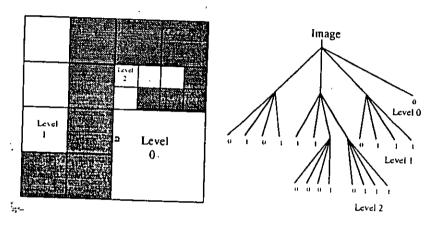

With this approach, parallelism is introduced by making use of any regular spatial geometry or structure present in the problem. Rather like a large cube may be divided up into a number of smaller constituent cubes, so the spatial geometry of the problem is divided up in some symmetrical fashion, assuming a uniform distribution of data over the geometry, to allow a more tractable solution to be expressed. Each of these small units acts as a quasi-independent entity, responsible for the data in its own spatial region. The computation performed by each small unit is summed to give an overall effect. Interactions between neighbouring units may be incorporated to give a more realistic solution. This approach is also known as data structure decomposition.

Each small unit is modelled by an identical occam parallel process, each parallel process operating on the data relevant to its own domain. Interactions between nearest neighbours may be introduced with occam channels connecting the neighbouring units. The communications overhead between these communicating processes may become quite appreciable.

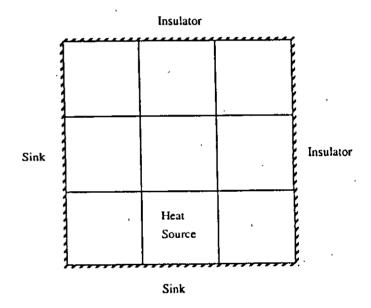

An example of the geometric approach is its use in the simulation of thermal conduction in a two-dimensional rectangular metal plate which is being heated by a heat source at a certain point. Simulation of thermal conduction over the whole plate is difficult. So, to simplify the problem, the geometry of the situation is utilised and the plate is subdifictor into a number of

Figure 11.1 A pipeline of processes to calculate the square root of a number using the Newton-Raphson method

The Newton-Raphson procedure may be written in a concurrent form by considering each iteration as an occam parallel process. Each of these processes accepts the number and previous estimate as input, calculates the new estimate and produces the number and new estimate as output (Figure 11.1). Thus the approximation technique may be written as a pipeline of identical processes with the necessary initialisation and termination processes. The pipeline may be generated with a replicated PAR statement. The top level of the program will have the following form

global declarations

procedures comprising

Initialisation process

Pipeline processes

Termination process

main process

The global declarations comprise the channels for the pipeline processes and the channels for the initialisation and termination processes. Assuming 50 iterations, this section may be written as

-- global declarations

VAL Iterations IS 50;

[Iterations + 1] CHAN OF REAL32 Pipe;

CHAN OF REAL32 InChan, OutChan;

The *Initialise* process inputs the number whose square root is required, and outputs the value of this number and initial square root estimate to the first pipeline process. This may be expressed in pseudo-code as

WHILE data is available

SEQ

INPUT a number

SEND this number and initial square root estimate to first pipeline process

In occam, this may be written as

PROC Initialise (CHAN OF REAL32 Input, Inject)

WHILE TRUE

REAL32 Number:

SEQ

Input? Number

-- feed number and initial estimate into pipeline

Inject! Number

Inject! Number / 2.0 (REAL32)

As indicated previously, the pipeline comprises *Iterations* identical processes which are generated with a PAR replicator. Each of these processes inputs the number and the previous estimate from the preceding pipeline process and outputs the number and new estimate to the succeeding process. Expressed in pseudo-code, this becomes

WHILE data is available

SEQ

RECEIVE a number and previous square root estimate from preceding pipeline process

SEND this number and new square root estimate to next pipeline process

rectangular areas - these areas being the quasi-independent units which will be represented by occam processes. The heat conduction i.e. temperature of each of these areas may be estimated and summed to give an approximate effect for the heat conduction over the whole plate. The temperature of each area will depend on that of its surroundings i.e. the neighbouring areas. It is assumed that one of the areas contains the heat source.

For the example, consider a metal plate, n by m units (Figure 11.2). The program is required to monitor the temperature at the centre of each of these areas. Also, for the example, consider that two boundaries (top and left-hand side) of the plate are adjacent to an infinite heat sink and that the other two boundaries (bottom and right-hand side) of the plate are adjacent to a perfect heat insulator.

The simulation program will comprise a set of identical parallel processes, each responsible for determining the temperature of one of the areas of the metal plate. This temperature is taken to be an average of the temperatures of the four neighbouring areas. In addition areas on the boundaries of the plate will be affected by the type of adjacent boundary - the heat sink will maintain a constant (base) temperature and the heat insulator will reflect the temperature of the boundary areas. These boundary effects will be simulated by extra parallel processes.

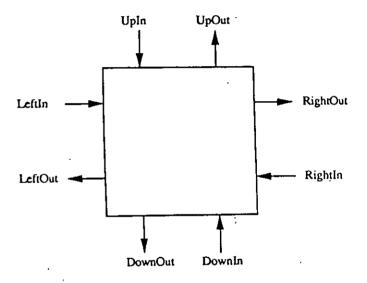

Each plate area will have nine channels - an input and output channel for each of the neighbouring areas, up, down, left and right plus a result channel (Figure 11.3). The result channel communicates with a monitor process to display the current temperature of each area on the screen.

There will be n \* m processes for calculating the areas' temperatures plus n + m processes for each of the two different boundary effects. This number of processes may be generated by suitable replication of the following processes

Sink - simulate the effect of a heat sink

Insulator - simulate the effect of a heat insulator

Source - simulate the effect of a heat source

CalcTemp - calculate the temperature of an area. Account must be taken of the fact that one of the areas will contain the heat source.

The top level of the program will have the following form

global declarations

procedures comprising

Sink

Insulator

Source

CalcTemp

main process

Figure 11.2 Metal plate subdivided into smaller areas

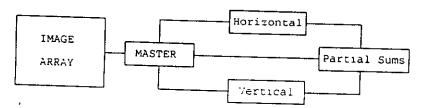

Assuming a metal plate of dimension 3 by 3 units, the global declarations are as follows

```

VAL Height IS 3:

VAL Width IS 3:

VAL TwiceHeight IS 2 * Height:

VAL TwiceWidth IS 2 * Width:

VAL Rectangle IS Height * Width:

VAL TwiceRectangle IS 2 * Rectangle:

VAL SourceX IS 1:

VAL SourceY IS 2:

VAL BaseTemp IS 50.0 (REAL32):

[TwiceRectangle + TwiceHeight] CHAN OF REAL32 Horizontal:

[TwiceRectangle + TwiceWidth] CHAN OF REAL32 Vertical:

[Rectangle] CHAN OF REAL32 Result:

```

The initial temperature, BaseTemp, is assumed to be 50 degrees. The position of the area containing the heat source at its centre is given by SourceX and SourceY. The areas communicate via the channels Horizontal, Vertical and Result. The horizontal channels are numbered in right/left pairs down the columns of the array of areas. The vertical channels are numbered in down/up pairs along the rows of the array. The result channels are numbered along the rows (see Figure 11.4 for an example of the 3 by 3 array).

The Sink process is simulated by maintaining (outputting) a constant temperature, regardless of the adjacent temperature - the temperature input is disregarded. This constant temperature is taken to be the initial temperature of the plate. Expressing this in pseudo-code gives

```

WHILE simulation is required

PAR

RECEIVE a temperature of an adjacent area and IGNORE

SEND a constant (base) temperature back to the adjacent area

```

Written as occam code, this gives

```

PROC Sink (CHAN OF REAL32 In, Out)

-- left or bottom boundary

WHILE TRUE

REAL32 Any:

PAR

-- ignore adjacent temperature

In ? Any

-- output a steady temperature

Out! BaseTemp

```

Figure 11.3 Channels of a plate area

The *Insulator* process does not allow any heat to escape - the temperature read from the adjacent area is returned. Written in pseudo-code, this is

WHILE simulation is required

SEQ

RECEIVE a temperature from an adjacent area

SEND the temperature received back to the adjacent area

#### Rewriting in occam gives

PROC Insulator (CHAN OF REAL32 In, Out)

-- top or right boundary

WHILE TRUE

REAL32 Temp:

SEQ

-- input temperature of adjacent area

In? Temp

-- return last temperature read

Out! Temp

Process Source simulates a heat source by generating a temperature which increases at a steady rate - one degree higher than the previous value. This temperature is transmitted to the surrounding areas, ignoring the present temperature of these areas. The heat source will be surrounded by four neighbouring areas. Expressing these requirements in pseudo-code gives

WHILE simulation is required

SEQ

PAR

RECEIVE a temperature from four surrounding areas and IGNORE

SEND new temperature back to four surrounding areas

INCREMENT temperature by one degree

Figure 11.4 The areas and channels for a 3 by 3 array

```

In occam, this may be written

PROC Source (CHAN OF REAL32 Upin, Downln, Leftin, Rightin,

UpOut, DownOut, LeftOut, RightOut,

Result)

VAL TempIncrease IS 1.0 (REAL32):

REAL32 Temp:

SEO

-- initial condition

Temp :- BaseTemp

WHILE TRUE

-- output new temperature to four surrounding areas, ignoring any inputs

SEO

PAR

REAL32 Any:

PAR

-- area below

Downin? Any

DownOut! Temp

REAL32 Anv:

PAR

-- area to left

Leftln? Any

LeftOut! Temp

REAL32 Any:

PAR

-- area above

Upin ? Any

UpOut! Temp

REAL32 Any:

PAR

-- area to right

Rightln 7 Any

RightOut! Temp

Result! Temp -- output new temperature to Monitor

Temp := Temp + TempIncrease -- increase temperature of source

```

(The interactions with each adjacent area have been grouped in separate PAR constructions for clarity)

Process CalcTemp will calculate the rise in temperature of each area due to the temperature of the neighbouring areas. Account must be taken of the fact that one area will contain the heat source. Written in pseudo-code, this is

```

IF area - heat source THEN

GENERATE temperature rise

ELSE

WHILE simulation is required

SEQ

PAR

RECEIVE the temperature of four surrounding areas

SEND the temperature of this area to four surrounding areas

CALCULATE new temperature of this area, based on temperature rises of surrounding areas

```

Expressing this pseudo-code in occam,

```

PROC CalcTemp (BOOL HotSpot,

CIIAN OF REAL32 Upin, Downin, Leftin, Rightin,

UpOut, DownOut, LeftOut, RightOut,

```

Result)

IF

-- if area contains heat source

HotSpot

-- generate temperature rise

Source (Upln, Downln, Leftln, Rightln,

UpOut, DownOut, LeftOut, RightOut, Result)

TRUE

-- area does not contain heat source

REAL32 Temp:

SEQ

-- initial conditions

Temp:= BaseTemp

```

WHILE TRUE

REAL32 SumOfTemps, MeanTemp,

UpTemp, DownTemp, LeftTemp, RightTemp,

DeltaUp, DeltaDown, DeltaLeft, DeltaRight:

SEO

-- interact with neighbouring areas

PAR

-- area below

PAR

Downin? DownTemp

DownOut! Temp

-- area to the left

PAR

LeftIn? LeftTemp

LeftOut! Temp

- area above

PAR

Upin ? UpTemp

UpOut! Temp

-- area to the right

PAR

Rightln? RightTemp

RightOut! Temp

DeltaDown := DownTemp - Temp

DeltaLeft := LeftTemp - Temp

DeltaUp := UpTemp · Temp

DeltaRight := RightTemp - Temp

-- now average these temperatures to find mean rise

SumOfTemps := ((DeltaUp + DeltaDown)

+ DeltaLeft) + DeltaRight

MeanTemp := SumOfTemps / 4.0 (REAL32)

-- increase temperature by half average temperature rise

Temp := Temp + (MeanTemp / 2.0 (REAL32))

-- output the result to Monitor

Result! Temp

```

```

WHILE simulation is required

SEO

PAR

INPUT temperature from each area

SEO

IF temperature o last temperature from each area THEN

DISPLAY temperature

Writing this in occam gives

PROC Monitor (1 | CHAN OF REAL32 Result)

[Rectangle] REAL32 LastTemp:

SEO

-- initialise array holding temperatures

SEQ Index = 0 FOR Rectangle

LastTemp [Index] := 0.0 (REAL32)

[Rectangle] REAL32 Temp:

WHILE TRUE

SEQ

-- input temperature of areas

PAR Index = 0 FOR Rectangle

Result [Index] ? Temp [Index]

SEQ Index = 0 FOR Rectangle

-- check for a temperature change

Temp [Index]   LastTemp [Index]

INT Row, Col:

SEO

-- display new temperature

Row := Index / Width

Col := Index REM Width

Display ! Row ; Col ; Temp [Index]

LastTemp [Index] := Temp [Index]

TRUE

SKIP

```

Process Monitor will be responsible for keeping a record of the temperature of each area, and

displaying this temperature on the screen. Expressing this in pseudo-code gives

The overall structure of the main process will be an outer PAR enclosing the requisite number of instances of *CalcTemp*, *Sink* and *Insulator* processes. In addition there will be an instance of the *Monitor* process. Thus the main process may be expressed in pseudo-occam as

#### PAR

Monitor process

n \* m CalcTemp processes

n + m Sink processes

n + m Insulator processes

This process may be rewritten in terms of nested replicated PARs (assuming n rows by m columns of rectangular areas - the index Row moving from top to bottom, the index Column moving from left to right) as follows

#### PAR

Monitor process

PAR Row = 0 FOR n -- left-hand side areas Sink process

PAR Column = 0 FOR m PAR

> - top side areas Insulator process

-- middle areas

PAR Row = 0 FOR n

CalcTemp process

-- bottom side areas Sink process

PAR Row = 0 FOR n -- right-hand side areas

Insulator process

Using the (more meaningful) constants Height (for n) and Width (for m) as specified in the global declarations, this may be rewritten as

```

PAR

Monitor (Result)

PAR Row = 0 FOR Height - left-hand side areas

VAL Out IS Row + Row:

VAL In IS Out + 1:

Sink (Horizontal [In], Horizontal [Out])

PAR Col = 0 FOR Width

PAR

-- top side areas

VAL Out IS Col + Col:

VAL In IS Out + 1:

Insulator (Vertical [In], Vertical (Out))

-- middle areas

PAR Row = 0 FOR Height

VAL Up IS ((TwiceWidth * Row) + Col) + Col:

VAL Down IS ((TwiceWidth * (Row + 1)) + Col) + Col:

VAL Left IS ((TwiceHeight * Col) + Row) + Row :

VAL Right IS ((TwiceHeight * (Col + 1)) + Row) + Row:

VAL Hot IS (Row = SourceY) AND (Col = SourceX):

SEQ

CalcTemp (Hot,

Vertical (Up).

Vertical [Down +1],

Horizontal (Left),

Horizontal [Right + 1],

Vertical [Up + 1],

Vertical [Down],

Horizontal [Left + 1],

```

Horizontal [Right],

Result [(Width \* Row) + Col])

-- bottom side areas

VAL In IS (TwiceRectangle + Col) + Col:

VAL Out IS In + 1:

Sink (Vertical [In], Vertical [Out])

PAR Row = 0 FOR Height -- right-hand side areas

VAL In IS (TwiceRectangle + Row) + Row:

VAL Out IS In + 1:

Insulator (Horizontal [In], Horizontal [Out])

Other examples of the use of this approach are the modelling of a statistical "spin" system as may be found in liquid crystal films [Askew et al.].

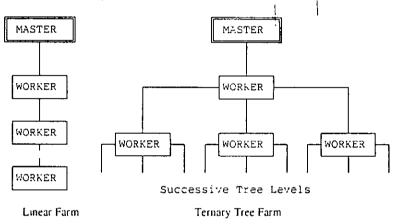

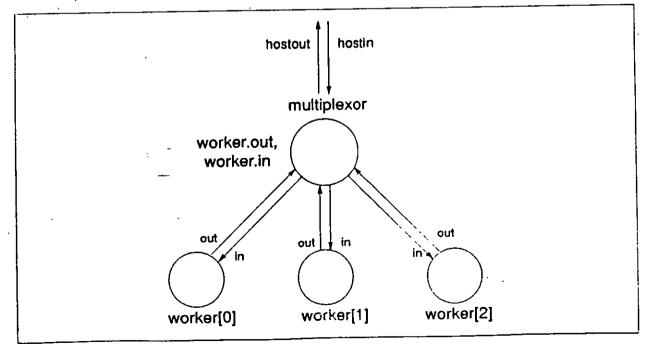

#### 11.3 Process farming

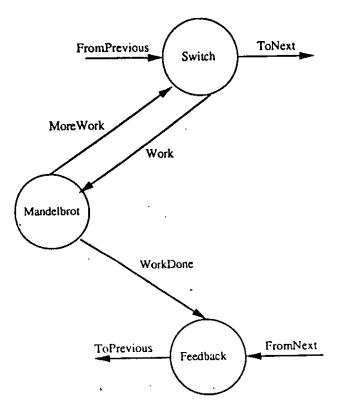

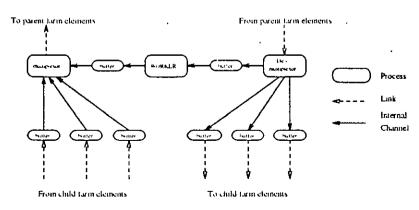

The farm approach is applicable to problems whose solution will succumb to a decomposition into many smaller parts and where these parts are independent of each other. As the parts are independent, each may be executed concurrently, in isolation, and the effect summed to give a solution to the whole problem. The solution is analogous to a farmer supervising the toil of many farm workers, each worker performing any given task in isolation from the other workers - hence the name.

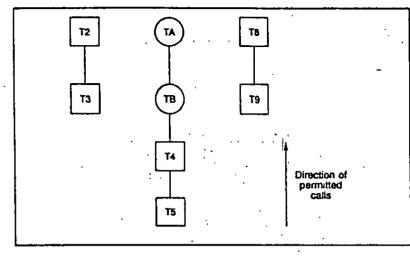

A farm is modelled by a set of occam processes. One process is nominated the farmer. The farmer process controls the organisation and allocation of work. The controlling process farms or hands out work to its subordinate worker processes. The worker processes are modelled as identical parallel occam processes. As and when each worker process completes the given task, the farmer process will issue further work for completion. Thus a farm of worker processes toil away on parts of the problem, finishing one task and starting another, until the whole problem is complete. Typically little inter-process communication is needed in such applications. However, depending on the number of worker processes and their configuration, for example whether they are organised in a linear or tree fashion, the routing of messages between the farmer and workers may well cause communications overhead problems.

An example of the process farm approach is its use in producing a graphical representation of the Mandelbrot set, or more exactly, a graphical representation of those points which lie within and without the Mandelbrot set [Barnsley et al., Peitgen and Richter]. This set comprises all complex numbers, c = a + ib, for which the recurrence relation

$$z_{n+1} = z_n^2 + c$$

for  $n = 0, 1, 2, ...$  (11.1)

converges to a finite complex number (where zn and zn+1 are complex numbers computed in

successive iterations of the recurrence relation, and  $z_0 = 0$  is the initial condition). It can be demonstrated that, if for some n,

$$|z_{-}| > 2$$

then the iteration diverges and hence c does not belong to the Mandelbrot set.

In practice, the iteration is performed a given number of times, m, and c is considered to belong to the Mandelbrot set, M, if

$$|z_n| < 2$$

for all  $n \le m$  (11.2)

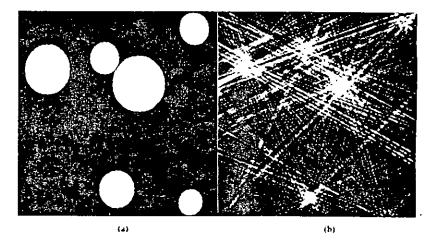

The graphical display of the members of M produces quite vivid and intriguing self-similar shapes known as fractals.

For display purposes, the complex number, c = a + ib, is taken to be a graphics screen pixel with coordinates (a,b) - the graphics screen representing the complex plane. For every screen pixel the recurrence relation is applied. If the pixel belongs to the Mandelbrot set, it is coloured black, otherwise it is allocated a colour from the graphics palette which is graded according to the speed at which the iteration diverges i.e. the smallest natural number n < m for which  $|z_n| \ge 2$ .

Such computation is quite intensive for a suitable number of iterations and, depending on the size of the graphics screen and hence the number of pixels, needs to be performed a large number of times. The actual computational task to be performed for each pixel is the same but the amount of computation will vary depending on whether or not the sequence of recurrence values for that pixel converges or diverges.

The general form of a farm in terms of pseudo-occam is as follows

global declarations PAR

\_\_\_\_

Farmer process

PAR Index = 0 FOR NumberOfWorkers

Worker process

Each worker process accepts data from the farmer process, works with this data and then sends the result back to the farmer process, becoming available to accept more data. In the current context this work will be the calculation of the recurrence relation for the given data i.e. pixel coordinates (a,b).

Assuming a graphics area of 512 by 512 pixels, with 50 workers, the global declarations section may be written as

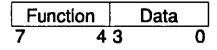

VAL NumberOfWorkers IS 50: VAL NumberOfPixels IS 512 \* 512 : PROTOCOL RAW CASE Data: 121 INT Terminate PROTOCOL PROCESSED

CASE Results: [2] INT: INT

Ouit

INumberOfWorkers + 11 CHAN OF RAW ToFarm: [NumberOfWorkers + 1] CHAN OF PROCESSED FromFarm:

The channels, ToFarm and FromFarm, allow the Farmer process to send data to the Worker processes and receive results from the Worker processes. The protocols, RAW and PROCESSED, will be explained shortly.

In practice, to improve the efficiency trade-off between computation and communications, each worker would be given a line of pixels as data. The processor overhead setting up a transmission over a transputer link is the same for many bytes as for a few bytes. (Once a data transfer has been initiated, the transfer of data over the link is automonous of the processor.) For simplicity, this example considers the data to be a single pixel. Also in practice, it may be advantageous to have a division of labour in the farmer process, having a farmer process proper and a separate graphics process. The function of the farmer process would be to hand out pixel coordinates to the worker processes, whilst that of the graphics process would be to accept the results (pixel coordinates and colour) and display them on the graphics screen.

Rather than allowing a worker process to idle whilst the farmer issues new work, the worker process may buffer an extra unit of work so that it may proceed immediately with this new work once it has completed the previous work. This scheme keeps the workers constantly busy [Packer].

Logically, each worker process may be connected via a channel to the farmer. Practically, since the transputer has only four links and if the workers are distributed over several transputers, there may be many tiers of worker processes. Because of this, each worker process will not just be concerned with the iteration of the recurrence relation. It will also act as a message switch, passing on data to processes further down the farm. The whole farm

process becomes self-regulating, message passing being synchronised by the occam input/output primitives. In addition to forwarding work to outlying workers, the worker process will gather results from these workers for onward delivery to the farmer (or graphics) process.

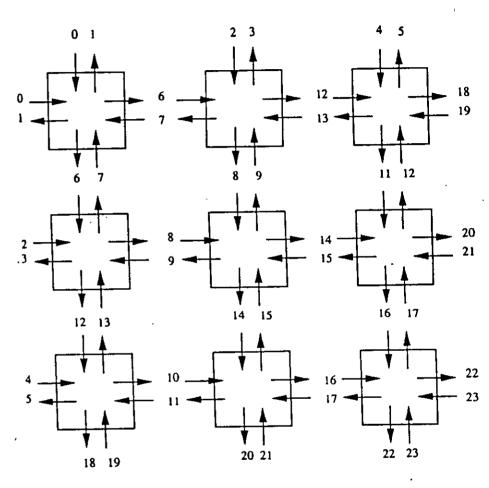

Each worker process will comprise three processes: Switch, Feedback and Mandelbrot (Figure 11.5). This arrangement may be expressed in pseudo-occam as

PROC Worker PRI PAR PAR Switch process Feedback process Mandelbrot process

This arrangement of processes in the PRI PAR construction ensures a high throughput for communications. This is important for processes which may use the transputer links, so that messages are transmitted without delay. If a high priority process was not used, the message would not be examined until the message switch was scheduled by the low priority round-robin scheduler of the transputer [May and Shepherd].

Tagged protocols, RAW and PROCESSED, are defined for the data which is sent to and received from the worker processes. The tag Data of protocol RAW corresponds to the transfer of two integers (a pixel), whilst the tag Results of protocol PROCESSED corresponds to the transfer of three integers (a pixel and its colour). In addition, each of these protocols has a tag which is used to pass a termination notice to the participating processes at the end of the calculation.

The Worker process may now be rewritten with the addition of channels.

PROC Worker (CHAN OF RAW FromPrevious, ToNext, CHAN OF PROCESSED ToPrevious. FromNext) CHAN OF BYTE MoreWork: CHAN OF RAW Work: CHAN OF PROCESSED WorkDone: PRI PAR PAR Switch (MoreWork, FromPrevious, ToNext, Work) Feedback (ToPrevious, FromNext, WorkDone) Mandelbrot (MoreWork, Work, WorkDone)

The Switch process is responsible for accepting pixels (work) from the Farmer process, buffering a pixel for its Mandelbrot process, and forwarding excess work to workers further

```

down the farm. Expressing this in pseudo-code gives

WHILE pixels are available

ALT

RECEIVE request from mandelbrot for another pixel

If buffer = full THEN

SEND buffered pixel to mandelbrot

ELSE

SET mandelbrot = idle

RECEIVE pixel from farmer

IF mandelbrot = idle THEN

SEND pixel to mandelbrot

ELSEIF buffer = empty

BUFFER pixel

ELSE

SEND pixel to next worker

```

Such a structure with more than one input to react to may be conveniently programmed using an ALT construction. The actual code will be slightly more complicated than the above pseudo-code owing to the need to watch out for and pass on the termination notice to the *Mandelbrot* process and the next worker. This is just a matter of reacting to the relevant tag of the channel protocol. The occam for the process is

```

PROC Switch (CHAN OF BYTE MoreWork,

CHAN OF RAW FromPrevious, ToNext, Work)

BOOL Busy, Buffered, Running:

SEQ

Busy := FALSE

Buffered :- FALSE

Running :- TRUE

WHILE Running OR Busy

[2] INT Coords, BufferedCoords:

BYTE Any:

ALT

-- mandelbrot requesting more work .

Busy & MoreWork? Any

IF

Buffered -- check for buffered work

-- pass mandelbrot the buffered work

SEO

Work! Data: BufferedCoords

Buffered :- FALSE

```

Figure 11.5 The component processes of a worker process

```

TRUE

-- no buffered work

Busy :- FALSE

- a message from the farmer

Running & FromPrevious ? CASE

Data; Coords - another pixel

NOT Busy

- check if mandelbrot busy

SEQ

Work! Data: Coords

Busy :- TRUE

NOT Buffered

- check if pixel buffered

SEO

BufferedCoords := Coords

Buffered :- TRUE

TRUE -- pass on pixel

ToNext! Data; Coords

Terminate

-- termination notice

Running := FALSE

ToNext! Terminate

-- pass on termination notice

Work! Terminate

```

In the above process, the boolean variable, Running, records whether or not a termination notice has been received from the farmer, whilst the boolean variable, Busy, marks whether or not the Mandelbrot process is processing a pixel. The Mandelbrot process performs the iteration procedure for a given pixel and assigns that pixel a colour dependent on the degree of convergence. With a little rearrangement the recurrence relation may be simplified for computation. Substituting z = x + iy, then equation (11.1) may be written as

$$x_{n+1} = x_n^2 - y_n^2 + a$$

and

$$y_{n+1} = 2x_ny_n + b$$

Since

$$|z_{n+1}| = \sqrt{x_{n+1}^2 + y_{n+1}^2}$$

the condition for Mandelbrot set occupancy - equation (11.2) - may be written as

$$x_{n+1}^2 + y_{n+1}^2 \le 4$$

Pixels are passed from the Switch process each time the Mandelbrot process completes the previous calculation and requires more work. Completed work, in terms of the pixel colour, is

```

passed on to the Feedback process. In pseudo-code, this gives

WHILE pixels are available

SEQ

RECEIVE pixel

loop:

CALCULATE next iteration of recurrence relation

IF iteration count - maximum THEN

ASSIGN black to colour

EXIT

IF modulus squared > constant THEN

ASSIGN count to colour

EXIT

```

SEND pixel and colour to feedback

Again the actual code will be complicated by the termination condition. This time the termination notice is passed on to the *Feedback* process. Expressed in occam (assuming a graphics palette of 256 colours, with the colour black having a value of 0, and a maximum number of iterations of 255), this gives

```

PROC Mandelbrot (CHAN OF BYTE MoreWork,

CHAN OF RAW Work.

CHAN OF PROCESSED WorkDone)

BOOL Running:

SEQ

Running := TRUE

WHILE Running

BYTE Any:

[2] INT Coords:

SEO

-- ask for some work

MoreWork! Any

Work ? CASE

- next set of coordinates

Data: Coords

VAL Constant IS 4.0 (REAL32):

VAL Two IS 2.0 (REAL32):

VAL MaxIterations IS 255:

VAL Black IS 0:

REAL32 A, B, X, Y, ZSquared:

INT Colour, Count:

```

```

SEQ

A := Coords [0]

B := Coords [1]

X := 0.0 (REAL32)

Y := 0.0 (REAL32)

Count := 0

ZSquared := 0.0 (REAL32)

- calculate next iteration of recurrence relation

- and test for divergence

WHILE (Count < MaxIterations) AND (ZSquared <= Constant)

SEO

X := ((X * X) - (Y * Y)) + A

Y := (Two * (X * Y)) + B

ZSquared := (X * X) + (Y * Y)

Count := Count + 1

IF

Count - MaxIterations -- pixel in Mandelbrot set

Colour := Black

ZSquared > Constant -- pixel outside Mandelbrot set

Colour := Count

WorkDone! Results; Coords; Colour

-- send results back

-- termination notice

Terminate

Running :- FALSE

-- pass on the termination notice

WorkDone! Quit

```

The Feedback process multiplexes the results from its Mandelbrot process and those received from other workers on the farm, and feeds them back to the Farmer process. Putting this in pseudo-code

```

WHILE pixels are available

ALT

RECEIVE pixel and colour from our worker

SEND pixel and colour back to graphics in

```

SEND pixel and colour back to graphics process RECEIVE pixel and colour from other workers

SEND pixel and colour back to graphics process

The code may be succinctly expressed in occam using an ALT construction. This time the treatment of the terminating condition needs more effort. The termination notice is only passed on when one has been received from both the local Mandelbrot process and the next worker [Jones and Goldsmith].

```

PROC Feedback (CHAN OF PROCESSED ToPrevious, FromNext, WorkDone)

[2] INT Coords:

INT Colour:

BOOL Local, Other:

SEQ

Local := TRUE

Other :- TRUE

WHILE Local OR Other

ALT

Local & WorkDone ? CASE

Results: Coords; Colour -- results from our worker

ToPrevious! Results; Coords; Colour -- pass back to farmer

Ouit -- termination notice from our worker

Local := FALSE

Other & FromNext ? CASE

-- results from another worker

Results; Coords; Colour

ToPrevious! Results; Coords; Colour -- pass back to farmer

Ourt -- termination notice from next worker

Other :- FALSE

ToPrevious ! Quit

-- pass on termination notice

```

In the above process boolean variables, Local and Other, record whether or not a termination notice has been received from the local worker or another worker respectively. Only when a termination notice has been received from both these processes does the Feedback process terminate.

A simplistic farmer process, which assumes that the farm is arranged as a chain of worker processes, is presented below. The farmer sends each pixel to the first worker in the chain for redistribution. The farm is primed by issuing 2\*NumberOfWorkers pixels to the work force. This amount of data just fills up each worker and each buffer. As each pixel is reported processed, another pixel is issued to the farm, until all the pixels have been processed [Atkin]. At this point a termination notice is issued to the farm of worker processes and the farmer waits to receive this back before finally terminating itself. In pseudo-code this is

```

PRIME farm with pixels

loop:

RECEIVE completed work from farm

SEND another pixel to fram

UNTIL pixels exhausted

```

The termination notice will pass down the chain of worker processes via the switch processes causing each switch process to terminate on receipt. Before terminating, each switch process will inform its mandelbrot process to terminate, which in turn will inform the feedback process of a local termination. When the termination notice reaches the end of the chain of worker processes, it must be returned to the farmer process via the feedback processes, causing each feedback, process to terminate (provided the local termination has also been received). Writing this in occam gives

```

PROC Farmer (CHAN OF RAW ToWorker,

CHAN OF PROCESSED FromWorker)

INT WorkDone, WorkWanted:

BOOL Running, Terminating:

SEQ

-- prime the farm

SEO Index = 0 FOR 2 * NumberOfWorkers

-- send pixel (row and column)

ToWorker! Data; [Index / 512, Index REM 512]

WorkDone := 2 * NumberOfWorkers

WorkWanted := 0

Running := TRUE

Terminating :- FALSE

WHILE Running

INT Colour:

[2] INT ResultCoords:

PRI ALT

From Worker ? CASE

-- receive completed work

Results; ResultCoords; Colour

SEQ

-- plot result

WorkWanted := WorkWanted + 1

Quit -- termination notice returned

Running :- FALSE

```

```

(WorkWanted > 0) & SKIP

IF

WorkDone < NumberOfPixels

SEQ

--- send another pixel

ToWorker ! Data ; [Index / 512, Index REM 512]

WorkDone := WorkDone + 1

WorkWanted := WorkWanted - 1

NOT Terminating

SEQ

Terminating := TRUE

ToWorker ! Terminate --- issue termination notice to farm

TRUE

SKIP

```

In the above process, the variable WorkDone keeps a count of the number of pixels processed, while the variable WorkWanted keeps a count of the number of pixels required to top up the farm.

The main process will comprise a PAR construction containing instances of the Farmer process and a number of replicated Worker processes. The last worker in the chain is a special case as it has no one else further down the chain to communicate with. A dummy process, EndStop, is provided to match the channels of this last worker so they are not left dangling. This dummy process accepts the termination notice from the switch process of the last worker (protocol RAW) and and generates a new one to pass back down the chain of feedback processes to the farmer (protocol PROCESSED) [Jones and Goldsmith].

```

PAR

Farmer (ToFarm [0], FromFarm [0])

PAR Index = 0 FOR NumberOfWorkers

Worker (ToFarm [Index], ToFarm [Index + 1],

FromFarm [Index], FromFarm [Index + 1])

EndStop (ToFarm [NumberOfWorkers], FromFarm [NumberOfWorkers])

```

An alternative to the dummy process approach is to treat the last worker separately [Packer]. This approach requires that the protocols RAW and PROCESSED be combined into one protocol, COMBINED, say.

```

PROTOCOL COMBINED

CASE

Data; [2] INT

Results; [2] INT; INT

Terminate

```

This means, of course, that the process and channel declarations, and the tag input and outputs must be altered accordingly. For example, the Worker process becomes

```

PROC Worker (CHAN OF COMBINED FromPrevious, ToNext,

ToPrevious, FromNext)

CHAN OF BYTE MoreWork:

CHAN OF COMBINED Work, WorkDone:

PRI PAR

PAR

Switch (MoreWork, FromPrevious, ToNext, Work)

Feedback (ToPrevious, FromNext, WorkDone)

Mandelbrot (MoreWork, Work, WorkDone)

```

and the Feedback process becomes

```

PROC Feedback (CHAN OF COMBINED ToPrevious, FromNext, WorkDone)

[2] INT Colour:

BOOL Local, Other:

SEQ

Local:= TRUE

Other:= TRUE

WHILE Local OR Other

ALT

Local & WorkDone? CASE

Results; Coords; Colour -- results from our worker

ToPrevious! Results: Coords; Colour -- pass back to farmer

Terminate -- termination notice from our worker

Local:= FALSE

```

Other & FromNext ? CASE

Results; Coords; Colour -- results from another worker

ToPrevious! Results; Coords; Colour -- pass back to farmer

Terminate -- termination notice from next worker

Other: = FALSE

ToPrevious! Terminate -- pass on termination notice

A special channel, LoopBack is declared as follows'

#### CHAN OF COMBINED LoopBack:

This channel is looped back in the last worker process to provide a return path for the termination notice.

```

PAR

Farmer (ToFarm [0], FromFarm [0])

PAR Index = 0 FOR NumberOfWorkers - 1

Worker (ToFarm [Index], ToFarm [Index + 1],

FromFarm [Index], FromFarm [Index + 1])

Worker (ToFarm [NumberOfWorkers], LoopBack

FromFarm [NumberOfWorkers], LoopBack)

```

Another example of process farming is its application to ray tracing to generate realistic images of scenes (Packer). Such an application requires considerable amounts of processing power. It has been shown that the processing speed is directly proportional to the number of transputers used for this generation of images.

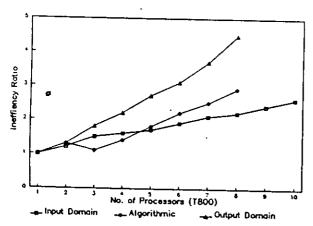

#### 11.4 Efficiency factors

Even after designing a parallel algorithm, there are a number of competing factors to be taken into consideration for an efficient implementation.

- processor connectivity the transputer has only four physical links.

Depending on the distribution of processes on processors, communications between processes may need to pass through several intervening transputers.

This routing of messages imposes an extra overhead on each transputer, and the balance between computation and communication needs to be carefully assessed.

- processor loading the processing load of each transputer in a "work must

be taken into consideration. The system is likely to run at the speed of the transputer with the highest processing load, as the other transputers in the system will probably be held up, waiting to communicate with this transputer. So the processing load should be shared as evenly as possible among the available transputers, and not left to chance or haphazard placement. The farm approach semi-dynamically balances the load for each processor, since a processor only receives more work when it becomes idle. The algorithmic approach needs especial care, as an overloaded processor may create a bottleneck in the pipeline or whatever configuration is chosen.

• processor type and memory - there are different types of transputer available with different word sizes and floating point capabilities. The choice of transputer for a particular function within a network needs to be carefully considered to match applications with suitable processors. For example, computation-bound tasks involving floating-point operations will obviously benefit from the use of a T800 processor. As regards memory, the program memory requirement must be balanced against the use of internal memory (fast but finite) and external memory.

# Métricas de Desempeño

# Measuring Parallel Processor Performance

Many metrics are used for measuring the performance of a parallel algorithm running on a parallel processor. This article introduces a new metric that has some advantages over the others. Its use is illustrated with data from the Linpack benchmark report and the winners of the Gordon Bell Award.

#### Alan H. Karp and Horace P. Flatt

There are many ways to measure the performance of a parallel algorithm running on a parallel processor. The most commonly used measurements are the elapsed time, price/performance, the speed-up, and the efficiency. This article defines another metric which reveals aspects of the performance that are not easily discerned from the other metrics.

The elapsed time to run a particular job on a given machine is the most important metric. A Cray Y-MP/1 solves the order 1,000 linear system in 2 17 seconds compared to 445 seconds for a Sequent Balance 21000 with 30 processors [2]. If you can afford the Cray and you spend most of your time factoring large matrices, then you should buy a Cray.

Price/performance of a parallel system is simply the elapsed time for a program divided by the cost of the machine that ran the job. It is important if there are a group of machines that are "fast enough." Given a fixed amount of money, it may be to your advantage to buy a number of slow machines rather than one fast machine. This is particularly true if you have many jobs to run and a limited budget. In the previous example, the Sequent Balance is a superior price/performer than the Cray if it costs less than 0.5 percent as much. On the other hand, if you can't wait 7 minutes for the answer, the Sequent is not a good buy even if it wins in price/performance.

These two measurements are used to help you decide what machine to buy. Once you have bought the machine, speed-up and efficiency are the measurements often used to let you know how effectively you are using it.

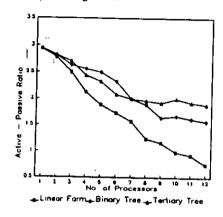

The speed-up is generally measured by running the same program on a varying number of processors. The speed-up is then the elapsed time needed by 1 processor divided by the time needed on p processors. s = T(1)/T(p). (Of course, the correct time for the uniprocessor run would be the time for the best serial algorithm, but almost nobody bothers to write two programs.) If you are interested in studying algorithms for

parallel processors, and system A gives a higher speedup than system B for the same program, then you would say that system A provides better support for parallelizing this program than does system B.